急问。怎样设constraint才能让DC报出下面几类interface的timing path.

时间:10-02

整理:3721RD

点击:

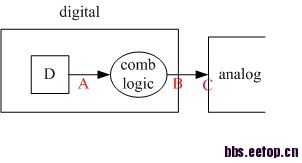

analog和digital的interface. analog就当成一个blackbox.

现在想要看以下几类path的timing.请问该如何约束。

digital 最后一级flop的输出到analog上对应的输入的timing.

analog边界上的输出,到digital 第一级flop输入。

另外还有个问题。set input/output delay是该设在port上。还是第一级flop上?port到flop之间还有一些组合逻辑。

如果是这种设计,一般情况下不会对数模接口的信号关心吧(对于a2d_sig在数字内部打两拍以后直接使用或检测有效沿再使用就可以了),

如果需要关心,则会有相关的随路时钟(或者说约束所需要的参照物吧)

现在想要看以下几类path的timing.请问该如何约束。

digital 最后一级flop的输出到analog上对应的输入的timing.

analog边界上的输出,到digital 第一级flop输入。

另外还有个问题。set input/output delay是该设在port上。还是第一级flop上?port到flop之间还有一些组合逻辑。

1) 直接report_timing -from/to 你想看的pin

2) 一般是port上

谢谢小编已经可以看到digital到analog boundary的path,但是显示没有 constraint.

请问这个constraint怎么设。是直接在digital 的input/output上设input/output delay吗。

谢谢

信息不够,无法回答

如上图所示。我要约束A到C这条path怎么办?

最好的方法是analog有一个完整的lib文件

如果没有的话,在C上set_output_delay试试

也可以试set_max_delay -from A -to C

或者什么都不加,就report_timing -from A -through B -to C -unconstraint,只要path delay符合你的要求就行了

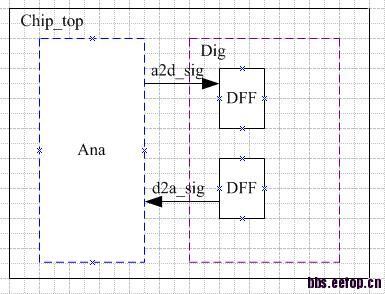

我想小编说的应该是下图所示的设计吧

如果是这种设计,一般情况下不会对数模接口的信号关心吧(对于a2d_sig在数字内部打两拍以后直接使用或检测有效沿再使用就可以了),

如果需要关心,则会有相关的随路时钟(或者说约束所需要的参照物吧)

多谢小编。

1. 如果是analog到digital 的path的话应该就是上面的方法反一反吧。

2. C已经是analog 的input了。直接在上面设output_delay吗?

3.完整的.lib文件里面的timing信息是不是就和综合库类似的,有定义timing的7X7矩阵?

还是说像ETM model一类?

如果是ICC的话,试试set_data_check -setup,然后report_timing。

encounter应该有类似的命令吧。

学习下 。

问题能说的详细一些么