verify出现的问题

时间:10-02

整理:3721RD

点击:

导入一个.def文件,刚开始用命令globalNetConnect和applyGlobalNets,然后做verify connect时,出现如下的ant问题,这是M1的P/G,

然后用verifyGeometry时,出现下图P/G的stripe的问题

我知道是P/G设置的问题可就是找不到问题所在

第一个图片

然后用verifyGeometry时,出现下图P/G的stripe的问题

我知道是P/G设置的问题可就是找不到问题所在

第一个图片

verify connect是ant问题;verify Geometry是short问题

ant问题是因为M1的rail 打叉端没有连到stripe上,形成了悬空。如果还没place,可以不管的,因为最后cell填满后就不会有悬空了。另一种简单的方法是再画条stripe把这些打叉的地方连起来,就OK啦。

short问题应该就是短路了,看看为什么电源和地会连起来吧。

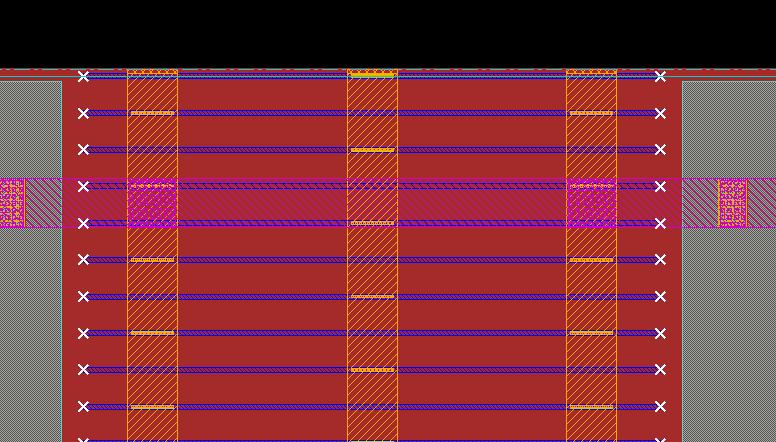

看图瞎猜,这个区域发生在两个IP之间,很可能是memory。然后def文件中只有floorplan,还没place。小编从power plan这一步开始做?

第一个确实是因为没有加FILLER造成的,在加FILLER的时候要把所有的placeblockage去掉吗?

第二个是VSS和VSS的short,VDD和VDD的short,不是VSS和VDD的short

第一 placeblockage是否去掉,取决于你的设计。第二 violation browers 可以帮你定位short发生的位置和层号。最好是能导个版图到calibre里面查,因为encounter有些时候会误报。