Verilog 综合后与自己设计的部分相结合的问题

时间:10-02

整理:3721RD

点击:

Verilog综合生成门级网表,那如果有一些电路是自己设计的,就是说不是代码生成的电路,比如说假如不用库里给出的D触发器,而全部用自己改进的D触发器,该如何实现呢?

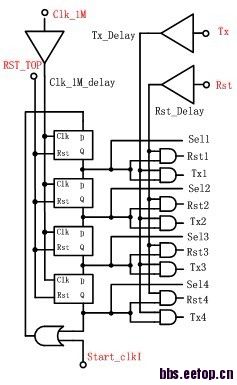

就这种结构,来实现下边的波形的每隔一段时间的复制。还有一种结构,叫guard gate,就是四个mos串联,上边2个pmos,下边2个nmos,p和n相连,代码也写不出来吧

如果有时序的要求,最好的办法是照猫画虎自己做一个lib

受教了

还是不太明吧,如果有些电路不能或者不容易用代码实现,那该怎么与Verilog生成的电路结合在一起呢?是在生成的门级网表里边写呢,还是自己画那部分电路的版图,然后和自动生成的版图拼在一起?

不一定需要完全用代码实现,只要做一个interface的timing就可以综合了

ni说的“有些电路不能或者不容易用代码实现”具体是指什么样的,这个没有固定的招法,但是没有做不出来的

就这种结构,来实现下边的波形的每隔一段时间的复制。还有一种结构,叫guard gate,就是四个mos串联,上边2个pmos,下边2个nmos,p和n相连,代码也写不出来吧

就是下边的波形是用verilog写出来的,用上面的结构生成几组相同的信号,只是每组相隔一段时间。(即图中红色的信号都由代码生成)这是图像传感器的时序控制里的,论文说用这种结构比用代码生成大量移位寄存器组省资源。那二者怎样实现对接呢?

还有一种结构,叫guard gate,就是四个mos串联,上边2个pmos,下边2个nmos,p和n相连,代码也写不出来吧.

如果你想DC把你手画的电路作为一个macro使用的话,你要写的是那些pin的时序关系,不是波形

如果你要DC给你综合出一个与你手画电路一样的东西出来,就另当别论了

让做这个电路的人,产生一个lib(具体什么工具,没问过相关人员),你用来综合,就像memory一样,

版图的时候合在一起就可以了