请教Astro之后由于CTS造成的延迟出现的时序问题

时间:10-02

整理:3721RD

点击:

如图1所示B模块输出时钟CLK和数据DATA,A模块接收B模块的输出CLK和DATA,A模块中的寄存器REG0使用时钟CLK对DATA进行锁存。

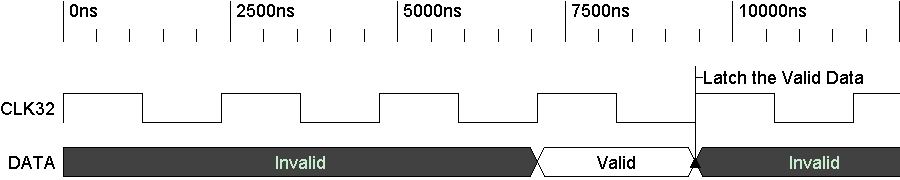

1.在功能模块以及前仿真时,我们的时序如图2所示,即Data的有效期(Valid)为一个CLK时钟周期(有对应的指示信号指示DATA有效),并且与CLK对齐,在图中所示的边沿REG0锁存到有效数据DATA;

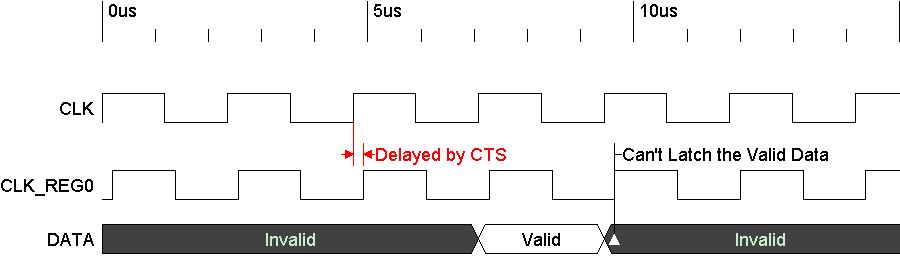

2.在Layout之后,由于插入了时钟树(CTS),导致了最后到达REG0时钟端的时钟(CLK_REG0)相对于原始时钟(CLK)有一定的延迟,而此时Data仍然与CLK对齐,结果导致了如图3所示的错误时序,即REG0不能在指定的边沿锁存到有效的数据。

请教各位如何解决这个问题(最好能够通过综合或者Astro Layout步骤解决这个问题。不太想改代码)。

我初步的想法是在数据输入端口(Data)插入延迟大于CTS造成的延迟的Buffer(REG0的Hold Time 为0),但是这个如何实现(是通过DC综合时或者SDC文件中增加时序约束--具体如何约束,还是通过Astro手动插入)

先谢谢各位了。

1.在功能模块以及前仿真时,我们的时序如图2所示,即Data的有效期(Valid)为一个CLK时钟周期(有对应的指示信号指示DATA有效),并且与CLK对齐,在图中所示的边沿REG0锁存到有效数据DATA;

2.在Layout之后,由于插入了时钟树(CTS),导致了最后到达REG0时钟端的时钟(CLK_REG0)相对于原始时钟(CLK)有一定的延迟,而此时Data仍然与CLK对齐,结果导致了如图3所示的错误时序,即REG0不能在指定的边沿锁存到有效的数据。

请教各位如何解决这个问题(最好能够通过综合或者Astro Layout步骤解决这个问题。不太想改代码)。

我初步的想法是在数据输入端口(Data)插入延迟大于CTS造成的延迟的Buffer(REG0的Hold Time 为0),但是这个如何实现(是通过DC综合时或者SDC文件中增加时序约束--具体如何约束,还是通过Astro手动插入)

先谢谢各位了。

我也不清楚,好像不好办啊。layout前你作sta了吗?对时钟网络的延迟是怎么评估的啊

在DC的时候设置的是 set_clock_latency = 0

Astro综合后由于时钟造成的延时在0.28-0.3ns左右

根据你的帮助,跑了一下PT做静态时序分析,确实出现了不少Hold Time的违背;

但是现在的问题是:

DC和Astro都没能够认出这些Hold Time违背,所以这些工具都没有去做fix hold violation;

1.请问一下造成这种PT认出Hold Time违背,而DC和Astro都未能认出违背的原因可能是什么?

2.如何设置可以使DC或者Astro认出这些Hold Time违背?

3.或者如何使用PT给出的时序信息进行Hold Time违背的修复?正在学习中

这个真的很难办

1。 把你的DC脚本贴出来看看,这样才容易找到问题。

2。 我觉得你的DC里面不应该设置set_clock_latency 0 CLK, 应该换成set_propagated_clock CLK,因为你已经综合了时钟树,应该用实际的延时。 set_clock_transistion也不需要设置。

我没做过,哈哈,也在学习中。,待高人解答。Dont set latency to 0

set_clock_latency = 0没关系,关键是set_clock_uncertainty -hold 参数要设置一般设为0.3,看实际需要而定

请问你的问题解决了吗,我也遇到和你一样的问题。最后那位朋友提供的方法不知道可以吗。现在去试试。