求助关于时钟结构

时间:10-02

整理:3721RD

点击:

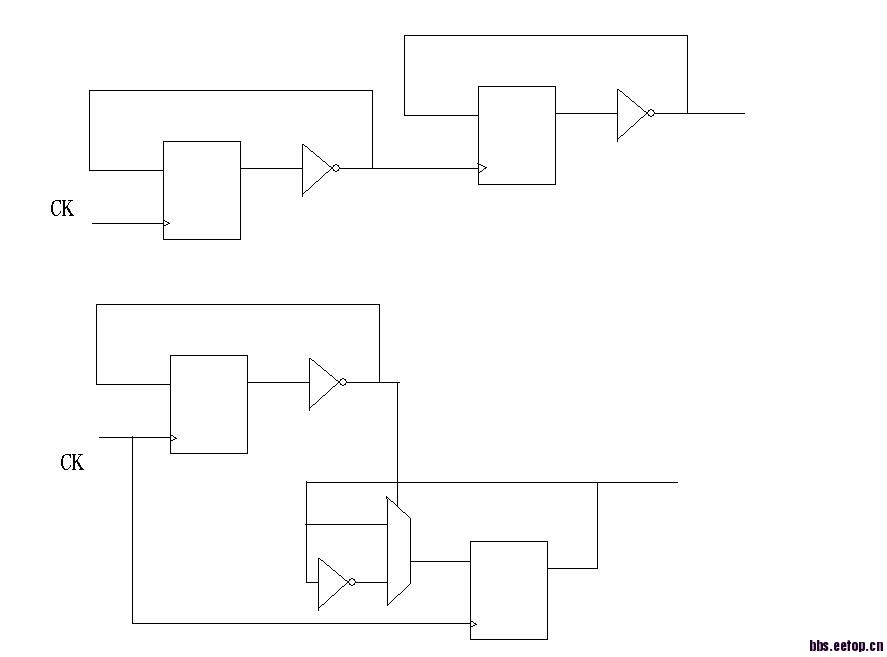

求助各位大牛,关于分频时钟结构,设计中一个模块使用四分频时钟(模块相对独立),请问该使用上图哪种分频模式更合适,直接四分频更合适还是使用二分频时钟作为使能端进行控制

另还有一个问题,寄存器作分频时看到过使用Q端连接反相器,或者使用QN端连接BUFFER进行分频,请问两种结构哪个更好?

谢谢各位大牛

直接四分频的比较好,容易设constraint

"使用Q端连接反相器与使用QN端连接BUFFER"只有微小的区别,基本上不用在意

ripple counter架构简单,但相位延迟较大,并且不同CLOCK DOMAIN间传输数据可能发生馈通现象

sync counter面积较大,但相位延迟较小,更容易控制

根据设计需求选择,很多时候整个系统中是两者的混合使用

谢谢老大解疑~

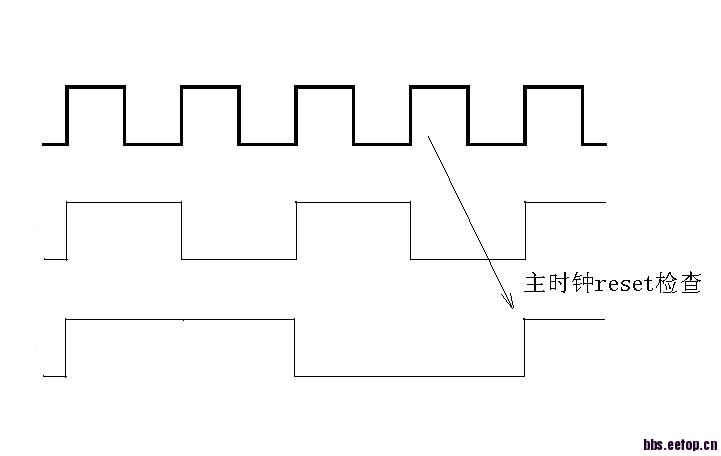

使用四分频时还遇到了一个问题,希望老大和各位大牛帮忙给看看

四分频后时钟周期增加,但是reset信号(经时钟同步)仍然属于主时钟域(快钟),因此reset信号的时序检查会变得很难满足,但是对于四分频钟并不需要那么快的reset,请问能否对该模块的reset信号设置multicycle?还是在端口处使用慢钟进行同步再作为子模块的reset更好?

复位经过采样后再给不同的时钟域用!

支持楼上!

这个问题说白了,就是异步数据处理:对DATA有SETUP/HOLD CHECK,对RESET有RECOVERY/REMOVAL CHECK,如果存在TIMING VIOLATION就说明设计有问题,除非是虚拟路径(false path)