calibre验证时产生的版图网表有错误

图1

图2

图3

通常LVS rule file跟PEX rule file會寫在一起。

建議您先diff 一下兩個檔案有啥差別

另外,可否貼一下LVS REDUCE區域的內容。

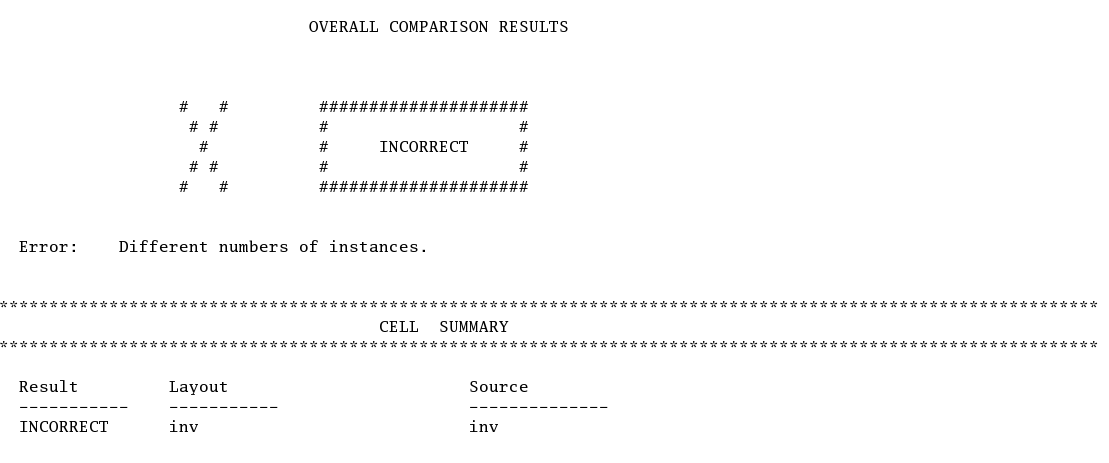

下面是LVS报告的全部内容:

##################################################

####

##C A L I B R ES Y S T E M##

####

##L V SR E P O R T##

####

##################################################

REPORT FILE NAME:lvs.rep

LAYOUT NAME:lay.sp ('inv')

SOURCE NAME:inv.src.net ('inv')

RULE FILE:HLMC_cl065lp_cal_v1p0_icrdcis.lvs

CREATION TIME:Fri Jan 10 15:40:27 2014

CURRENT DIRECTORY:/home/C63/process/HLMC55/PEX

USER NAME:C63

CALIBRE VERSION:v2010.3_28.18Wed Sep 1 21:48:33 PDT 2010

OVERALLCOMPARISON RESULTS

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Different numbers ofinstances.

**************************************************************************************************************

CELLSUMMARY

**************************************************************************************************************

ResultLayoutSource

------------------------------------

INCORRECTinvinv

**************************************************************************************************************

LVSPARAMETERS

**************************************************************************************************************

o LVS Setup:

//LVS COMPONENT TYPE PROPERTY

//LVS COMPONENT SUBTYPE PROPERTY

//LVS PIN NAME PROPERTY

LVS POWER NAME"?VDD?""?VCC?"

LVS GROUND NAME"?VSS?" "?GND?"

LVS CELL SUPPLYNO

LVS RECOGNIZE GATESNONE

LVS IGNORE PORTSNO

LVS CHECK PORT NAMESYES

LVS IGNORE TRIVIAL NAMED PORTSNO

LVS BUILTIN DEVICE PIN SWAPYES

LVS ALL CAPACITOR PINS SWAPPABLEYES

LVS DISCARD PINS BY DEVICENO

LVS SOFT SUBSTRATE PINSNO

LVSINJECT LOGICNO

LVS EXPAND UNBALANCED CELLSYES

LVS EXPAND SEED PROMOTIONSNO

LVS PRESERVE PARAMETERIZED CELLSNO

LVS GLOBALS ARE PORTSYES

LVS REVERSE WLNO

LVS SPICE PREFER PINSYES

LVS SPICE SLASH IS SPACEYES

LVS SPICE ALLOW FLOATING PINSYES

//LVS SPICE ALLOW INLINE PARAMETERS

LVS SPICE ALLOW UNQUOTED STRINGSNO

LVS SPICE CONDITIONAL LDDNO

LVS SPICE CULL PRIMITIVE SUBCIRCUITSNO

LVS SPICE IMPLIED MOS AREANO

//LVS SPICE MULTIPLIER NAME

LVS SPICE OVERRIDE GLOBALSNO

LVS SPICE REDEFINE PARAMNO

LVS SPICE REPLICATE DEVICESNO

LVS SPICE SCALE X PARAMETERSNO

LVS SPICE STRICT WLNO

//LVS SPICE OPTION

LVS STRICT SUBTYPESNO

LVS EXACT SUBTYPESNO

LAYOUT CASENO

SOURCE CASENO

LVS COMPARE CASENO

LVS DOWNCASE DEVICENO

LVS REPORT MAXIMUM50

LVS PROPERTY RESOLUTION MAXIMUM65536

//LVS SIGNATURE MAXIMUM

LVS FILTER UNUSED OPTIONAB RC RE RG

LVS REPORT OPTIONA B C D S

LVS REPORT UNITSYES

//LVS NON USER NAME PORT

//LVS NON USER NAME NET

//LVS NON USER NAME INSTANCE

//Device Type Map

LVS DEVICE TYPENMOS "n12_lp" "nlvt12_lp" "nhvt12_lp""nt12_lp" SOURCE LAYOUT

LVS DEVICE TYPEPMOS "p12_lp" "plvt12_lp" "phvt12_lp"SOURCE LAYOUT

LVS DEVICE TYPENMOS "n33_lp""p33_lp" "n25od33_lp" "p25od33_lp""nt25_lp" SOURCE LAYOUT

LVS DEVICE TYPEBIPOLAR "pnp12a4_lp" "pnp12a25_lp""pnp12a100_lp" "npn12a4_lp" "npn12a25_lp"

"npn12a100_lp" SOURCELAYOUT

LVS DEVICE TYPEBIPOLAR "pnp25a4_lp" "pnp25a25_lp""pnp25a100_lp" "npn25a4_lp" "npn25a25_lp"

"npn25a100_lp" SOURCE LAYOUT

LVS DEVICE TYPEBIPOLAR "pnp10_3""pnp5_3" "pnp2_3" SOURCE LAYOUT

LVS DEVICE TYPERESISTOR "res_ndif" "res_pdif" "res_npo""res_ppo" "res_ndifsab" "res_pdifsab"

"res_nposab" "res_pposab" "res_nwaa""res_nwsti" [ POS=plus NEG=minus ] SOURCE LAYOUT

LVS DEVICE TYPERESISTOR "res_m1" "res_m2" "res_m3" [POS=plus NEG=minus ]SOURCE LAYOUT

LVS DEVICE TYPERESISTOR "res_t2m1" [ POS=plus NEG=minus ]SOURCE LAYOUT

LVS DEVICE TYPERESISTOR "res_alpa" [ POS=plus NEG=minus ]SOURCE LAYOUT

LVS DEVICE TYPECAPACITOR "mom13" [ POS=n1 NEG=n2 ]SOURCE LAYOUT

LVS DEVICE TYPECAPACITOR "n12var_lp""p12var_lp" "n25var_lp" "p25var_lp" [ POS=plusNEG=minus ]SOURCE LAYOUT

//Reduction

LVS REDUCE SERIES MOSNO

LVS REDUCE PARALLEL MOSYES

LVS REDUCE SEMI SERIES MOSNO

LVS REDUCE SPLIT GATESYES

LVS REDUCE PARALLEL BIPOLARYES

LVS REDUCE SERIES CAPACITORSYES

LVS REDUCE PARALLEL CAPACITORSYES

LVS REDUCE SERIES RESISTORSYES

LVS REDUCE PARALLEL RESISTORSYES

LVS REDUCE PARALLEL DIODESYES

LVS REDUCEres_ndifSERIES plus minus

LVS REDUCEres_ndifPARALLEL

LVS REDUCEres_pdifSERIES plus minus

LVS REDUCEres_pdifPARALLEL

LVS REDUCEres_npoSERIES plus minus

LVS REDUCEres_npoPARALLEL

LVS REDUCEres_ppoSERIES plus minus

LVS REDUCEres_ppoPARALLEL

LVS REDUCEres_ndifsabSERIES plus minus

LVS REDUCEres_ndifsabPARALLEL

LVS REDUCEres_pdifsabSERIES plus minus

LVS REDUCEres_pdifsabPARALLEL

LVS REDUCEres_nposabSERIES plus minus

LVS REDUCEres_nposabPARALLEL

LVS REDUCEres_pposabSERIES plus minus

LVS REDUCEres_pposabPARALLEL

LVS REDUCEres_nwaaSERIES plus minus

LVS REDUCEres_nwaaPARALLEL

LVS REDUCEres_nwstiSERIES plus minus

LVS REDUCEres_nwstiPARALLEL

LVS REDUCEres_m1SERIES plus minus

LVS REDUCEres_m1PARALLEL

LVS REDUCEres_m2SERIES plus minus

LVS REDUCEres_m2PARALLEL

LVS REDUCEres_m3SERIES plus minus

LVS REDUCEres_m3PARALLEL

LVS REDUCEres_t2m1SERIES plus minus

LVS REDUCEres_t2m1PARALLEL

LVS REDUCEres_alpaSERIES plus minus

LVS REDUCEres_alpaPARALLEL

LVS REDUCEmom13SERIES n1 n2

LVS REDUCEmom13PARALLEL

LVS REDUCEn12var_lpPARALLEL

LVS REDUCEp12var_lpPARALLEL

LVS REDUCEn25var_lpPARALLEL

LVS REDUCEp25var_lpPARALLEL

LVS REDUCTION PRIORITYPARALLEL

//Trace Property

TRACE PROPERTYnpdw w 0

TRACE PROPERTYnpdl l 0

TRACE PROPERTYnpgw w 0

TRACE PROPERTYnpgl l 0

TRACE PROPERTYppuw w 0

TRACE PROPERTYppul l 0

TRACE PROPERTYdp_npdw w 0

TRACE PROPERTYdp_npdl l 0

TRACE PROPERTYdp_npg1w w 0

TRACEPROPERTYdp_npg1l l 0

TRACE PROPERTYdp_npg2w w 0

TRACE PROPERTYdp_npg2l l 0

TRACE PROPERTYdp_ppuw w 0

TRACE PROPERTYdp_ppul l 0

TRACE PROPERTYn12_lpw w 0

TRACE PROPERTYn12_lpl l 0

TRACE PROPERTYp12_lpw w 0

TRACE PROPERTYp12_lpl l 0

TRACE PROPERTYnlvt12_lpw w 0

TRACE PROPERTYnlvt12_lpl l 0

TRACE PROPERTYplvt12_lpw w 0

TRACE PROPERTYplvt12_lpl l 0

TRACE PROPERTYnhvt12_lpw w 0

TRACE PROPERTYnhvt12_lpl l 0

TRACE PROPERTYphvt12_lpw w 0

TRACE PROPERTYphvt12_lpl l 0

TRACE PROPERTYnt12_lpw w 0

TRACE PROPERTYnt12_lpl l 0

TRACE PROPERTYn33_lpw w 0

TRACE PROPERTYn33_lpl l 0

TRACE PROPERTYp33_lpw w 0

TRACE PROPERTYp33_lpl l 0

TRACE PROPERTYn25od33_lpw w 0

TRACE PROPERTYn25od33_lpl l 0

TRACE PROPERTYp25od33_lpw w 0

TRACE PROPERTYp25od33_lpl l 0

TRACE PROPERTYnt25_lpw w 0

TRACE PROPERTYnt25_lpl l 0

TRACE PROPERTYda a 0

TRACE PROPERTYdp p 0

TRACE PROPERTYres_ndifw w 0

TRACE PROPERTYres_ndifl l 0

TRACE PROPERTYres_pdifw w 0

TRACE PROPERTYres_pdifl l 0

TRACE PROPERTYres_npow w 0

TRACE PROPERTYres_npol l 0

TRACE PROPERTYres_ppow w 0

TRACE PROPERTYres_ppol l 0

TRACE PROPERTYres_ndifsabw w 0

TRACE PROPERTYres_ndifsabl l 0

TRACE PROPERTYres_pdifsabw w 0

TRACE PROPERTYres_pdifsabl l 0

TRACE PROPERTYres_nposabw w 0

TRACE PROPERTYres_nposabl l 0

TRACE PROPERTYres_pposabw w 0

TRACE PROPERTYres_pposabl l 0

TRACE PROPERTYres_nwaaw w 0

TRACE PROPERTYres_nwaal l 0

TRACE PROPERTYres_nwstiw w 0

TRACE PROPERTYres_nwstil l 0

TRACE PROPERTYres_m1w w 0

TRACE PROPERTYres_m1l l 0

TRACE PROPERTYres_m2w w 0

TRACE PROPERTYres_m2l l 0

TRACE PROPERTYres_m3w w 0

TRACE PROPERTYres_m3l l 0

TRACE PROPERTYres_t2m1w w 0

TRACE PROPERTYres_t2m1l l 0

TRACEPROPERTYres_alpaw w 0

TRACE PROPERTYres_alpal l 0

TRACE PROPERTYmom13n n 0

TRACE PROPERTYn12var_lpw w 0

TRACE PROPERTYn12var_lpl l 0

TRACE PROPERTYp12var_lpw w 0

TRACE PROPERTYp12var_lpl l 0

TRACE PROPERTYn25var_lpw w 0

TRACE PROPERTYn25var_lpl l 0

TRACE PROPERTYp25var_lpw w 0

TRACE PROPERTYp25var_lpl l 0

CELL COMPARISON RESULTS (TOP LEVEL )

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Different numbers ofinstances (see below).

LAYOUT CELL NAME:inv

SOURCE CELL NAME:inv

--------------------------------------------------------------------------------------------------------------

NUMBERS OF OBJECTS

------------------

LayoutSourceComponent Type

--------------------------

Ports:44

Nets:44

Instances:01*MN (4 pins)

10*n33_lp (4 pins)

10*p33_lp (4 pins)

01*MP (4 pins)

------------

Total Inst:22

* = Number of objects in layout different from number in source.

**************************************************************************************************************

INCORRECTOBJECTS

**************************************************************************************************************

LEGEND:

-------

ne= Naming Error (same layoutname found in source

circuit, but object was matched otherwise).

**************************************************************************************************************

INCORRECTINSTANCES

DISC# LAYOUT NAMESOURCE NAME

**************************************************************************************************************

1X0(0.390,-0.085)n33_lp** missinginstance **

G: IN** IN **

S: OUT** OUT **

D: GND**GND **

B: GND** GND **

--------------------------------------------------------------------------------------------------------------

2X1(0.440,1.575)p33_lp** missinginstance **

G: IN** IN **

S: OUT** OUT **

D: VDD** VDD**

B: VDD** VDD **

--------------------------------------------------------------------------------------------------------------

3** missing instance **MM0MP(P33_LP)

** IN **g: IN

** VDD **s: VDD

** OUT **d: OUT

** VDD **b: VDD

--------------------------------------------------------------------------------------------------------------

4** missing instance **MM1MN(N33_LP)

** IN **g: IN

** GND **s: GND

** OUT **d: OUT

** GND **b: GND

**************************************************************************************************************

INFORMATION ANDWARNINGS

**************************************************************************************************************

MatchedMatchedUnmatchedUnmatchedComponent

LayoutSourceLayoutSourceType

-----------------------------------------

Ports:4400

Nets:4400

Instances:0001MN(N33_LP)

0010n33_lp

0010p33_lp

0001MP(P33_LP)

--------------------------------

Total Inst:0022

o Initial Correspondence Points:

Ports:VDD GND IN OUT

**************************************************************************************************************

SUMMARY

**************************************************************************************************************

Total CPU Time:0 sec

Total Elapsed Time:0 sec

X代表是一個SUBCKT,所以用了X,就要寫一個相對應的SUBCKT給他。

所以用M是對的!

因為你只是要一個mos。

另外,建議您將netlist裡面的p33_lp、n33_lp換成大寫!

现在是我的版图网表会自动产生的是X开头,这样就跑不过,改成M就可以跑过,我不知道是什么原因会导致它产生错误

calibre系统是有一些关键词的,以M开头的代表为MOS管,X开头的为子电路。如4楼所说,要是器件以X开头,你需要给他一个子电路。

我也遇到这问题,版图网表在哪里改啊?从来没注意过网表的事情………

calibre pex-->input-->H Cells-->`Match cells by name`untick that item

还可以改网表器件的类型吗?怎么改?