virtuoso版图设计

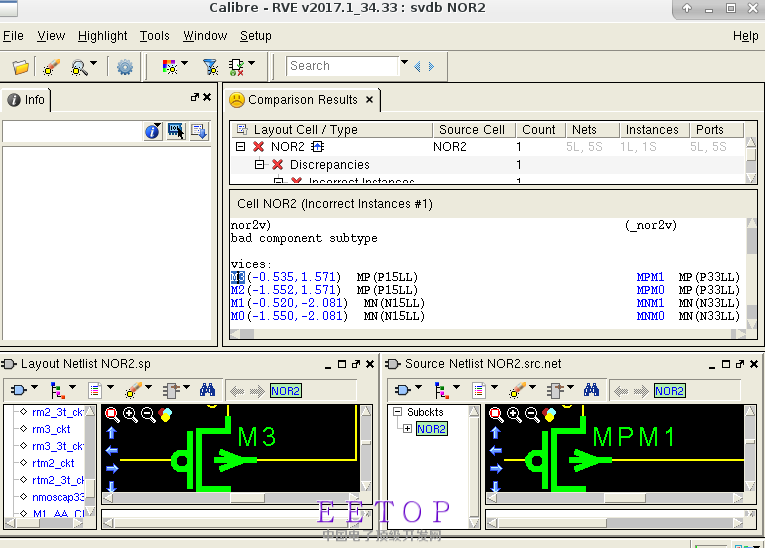

这个是报错

P15LLP33LL MOS type 不对

我知道是那个地方名字对不上号,但是我不知道怎么改

器件类型不一样,改成一致的就好了

应该只是一个layer用的不对,你可以看下PDK 中 这俩MOS的区别。

要么就是没有PDK 要么就是有PDK 但使用不规范。不然不会出现这种问题的。

如果你是要自己画逻辑单元,那么开工前基本连器件类型都不能区别,还怎么画呀?个人建议你规范你的工作习惯,如果你想继续在layout方面搬砖。

如果单单是希望lvs 同而不管真实的前端器件需求的话改法很多,问什么强大前面在话之前要增大机器的区别。就是怕有部分人知道了其他的方法就去改了 LVS 过了 但是不是前端需要的,这种方法就有比如 1 改cdl 网表,2 改lvs rule 文件,这是很可怕的如果你们做的产品里面只有这种电压的时候那么一直到最后tapeout 都不能发现这个问题,如果你们的工艺厂里面的接口工程师是神级队友还与可能帮你们检查出来,可是 如果不是神级队友呢,最后结果只能呵呵 了。即使神级队友出现了还有一种可能是数据重新出,这时候问题就来了 如果在DRC上面不同电压的器件没区别还好,如果是有区别的话呢?结果 就是 可能你们要重新画的机会比较大了。

还有一种改法其实就是楼上同学说的 差一些层,如果只是简单的差一层两层还好最多就是把层加上去之后就不用怎么改了,不同电压类型的器件的这种差别的工艺大部分DRC 都是没多大差别的。如果有些是在结果上还有区别的那么你也是要重新画,但也这是对于单元级,返工的量不多还好。其实知道前端使用器件的结构是必须的,你不想自己老是返工。

规范好自己的工作习惯吧。

感谢你的知道,今天我已经把问题找到了,是缺了一个DG层,有那层才算是3.3V的管子。不过对于你所说的规范习惯问题我表示赞同,因为越往后面习惯问题越重要,特别是这种繁琐的问题,一旦出现因为习惯导致的问题那整个版图估计就要重新画了。本人也是新人,对于画版图这方面的习惯确实不是特别了解,还希望你指点一下,就版图这块习惯问题,画版图要怎样一个习惯或方式去做才是正确的习惯!谢谢,感激不尽!