版图设计中的几个疑问。

时间:10-02

整理:3721RD

点击:

大家好。本人是一名菜鸟。这是我在此论坛发的第一篇帖子。

本人在学习SMIC 180nm的规则的时候,遇到了一些不明之处。还望各位指点一二。

1.N阱、P阱、AA划分?

根据相关的工艺介绍,此工艺是双阱工艺,先制作AA区窗口,然后分别注入相应的离子形成N阱和P阱。但是版图介绍中没有介绍P阱规则,只有N阱规则。

问:是否N阱外的地方都需要注入相应的粒子形成P阱?或者直接用P衬底做P阱?

2.GT规则?

所有的带有ct的GT必须是salicide poly吗?例如下面的描述中所说的GT.

GT.10 a:maximum length of silicide poly on STI between two contacts when poly width <=0.24μm;

GT.10b: maximum length of silicide poly on STI between one contact and poly line end when poly width <=0.24μm

3.关于NLL(或NLH),PLL(或PLH)掩膜版图.

貌似工艺里面有这些层沿模板,但是我看同事画的版图中没有这几层。

请问这是怎么回事。没有画出代表这些图层不是必需的还是工艺厂商得到版图后会自动加上这些层?

4. 关于SAB。即salicide block层。

也是很多版图中没有画出。请问,没有画出代表此图层不是必需的还是工艺厂商会自动加上这一层?

小弟新人,有表述不当之处还请谅解。

希望有热心的朋友赐教。也欢迎各位只对自己熟悉或者感兴趣的问题回答。小弟在这里谢过了。

本人在学习SMIC 180nm的规则的时候,遇到了一些不明之处。还望各位指点一二。

1.N阱、P阱、AA划分?

根据相关的工艺介绍,此工艺是双阱工艺,先制作AA区窗口,然后分别注入相应的离子形成N阱和P阱。但是版图介绍中没有介绍P阱规则,只有N阱规则。

问:是否N阱外的地方都需要注入相应的粒子形成P阱?或者直接用P衬底做P阱?

2.GT规则?

所有的带有ct的GT必须是salicide poly吗?例如下面的描述中所说的GT.

GT.10 a:maximum length of silicide poly on STI between two contacts when poly width <=0.24μm;

GT.10b: maximum length of silicide poly on STI between one contact and poly line end when poly width <=0.24μm

3.关于NLL(或NLH),PLL(或PLH)掩膜版图.

貌似工艺里面有这些层沿模板,但是我看同事画的版图中没有这几层。

请问这是怎么回事。没有画出代表这些图层不是必需的还是工艺厂商得到版图后会自动加上这些层?

4. 关于SAB。即salicide block层。

也是很多版图中没有画出。请问,没有画出代表此图层不是必需的还是工艺厂商会自动加上这一层?

小弟新人,有表述不当之处还请谅解。

希望有热心的朋友赐教。也欢迎各位只对自己熟悉或者感兴趣的问题回答。小弟在这里谢过了。

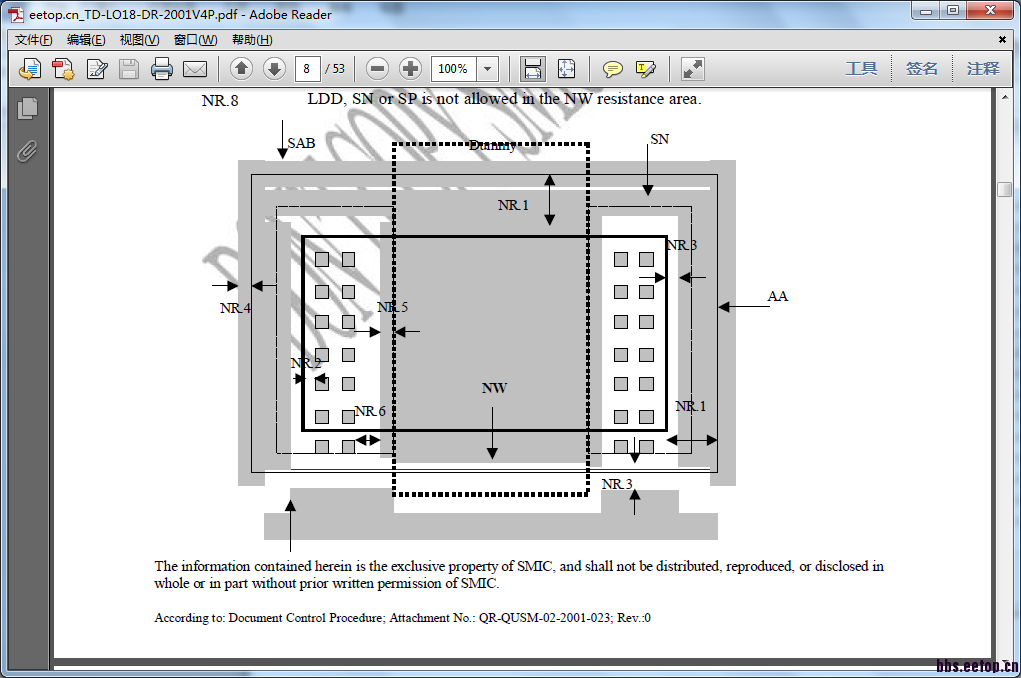

N阱电阻

不好 意思。多贴了一张照片。本来是准备问另一个问题用的。sorry!

还是多看书,看资料吧。

1.你说的这种只能是称单阱工艺,你的P阱就是P衬底,之所以叫阱,是因为会做阈值调整,所以跟原衬底不一样了。

2.未必所有的ct都做salicide,要看要求电阻的要求。高阻肯定不用

3.不知道你这3层是什么,你又没给描述

4.你也说是有的地方没画,有的地方画了,看不出这有什么不对。

多谢了,获益良多。呵呵。

24两个问题可以一起回答:工艺默认做salicide ,如果不做的地方就用SAB框起来.

多谢多谢。

看foundry doc

怎么才在学0.18啊

pwell可不是最底层的wafer,最底层的是用作ZMOS的衬底的,普通nmos是做在注入的pwell上的。

3.关于NLL(或NLH),PLL(或PLH)掩膜版图.

貌似工艺里面有这些层沿模板,但是我看同事画的版图中没有这几层。

请问这是怎么回事。没有画出代表这些图层不是必需的还是工艺厂商得到版图后会自动加上这些层?

NLL和PLL是根据你版图中现有的层次做掩膜版时用布林运算产生出来的。你在版图上是不需要画的。

建议你看下Mask Tooling这个文档

学习学习!

共同学习下

感觉都好厉害啊,我这么多年什么都没学会

飘过---