超深亚微米工艺下的SRAM版图设计求助

时间:10-02

整理:3721RD

点击:

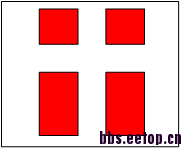

在研究关于SRAM版图cell设计的时候发现,90nm工艺下的SRAM中6管中4个双稳态锁存管的分布大致如下,上面两个为PMOS,下面两个为NMOS

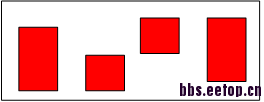

但是看到65nm工艺下的大致分布如下中间为两个PMOS,两边为两个NMOS,看到有45nm工艺的也大致如下图所示

我想问一下这样设计的目的是为什么,是因为65nm下图中的版图设计方式面积最省吗?还是还有其他原因,考虑到其他因素

不知道关于SRAM版图的设计到应该在哪里求助?希望大神指点

有和小编一样的疑问,同问,有哪位大牛有Memory 版图方面的资料,谢谢!

130nm以上一般使用'tall'型bitcell,面积更小,130nm以下考虑到光刻偏差,采用"fat"型bitcell,这样poly都是条状并且方向一致,良率高但面积稍微大一点。当然这些都是6T bitcell

谢谢大神指点,那对于6T单元的常见版图布局就是以上两种吗?还是还有别的,他们各自的优缺点是什么?劳烦大神再指点,或者有相关资料也行

一些公司提供自己的bitcell,但主流6T就这两种。

学习了!