带单独高压管脚的ESD电路的设计

时间:10-02

整理:3721RD

点击:

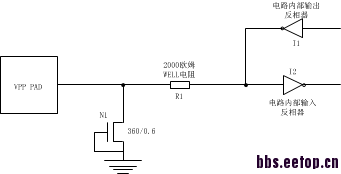

我设计一个OTP的产品,OTP烧录的时候,需要额外用一个VPP的高压管脚来提供高压来进行烧写OTP单元;也就是说这个管脚没办法设计通常的PMOS管来做ESD保护了;现在这个管脚只做了NMOS保护,没做PMOS保护,但现在出来的芯片显示这个管脚的ESD特别差;不知道大家对这样的电路该如何设计ESD保护?

vpp pad通常是特殊的pad啊,可以耐高压

再说了,vpp通常不封装出来的啊,只用于otp,flash调试用, 你要测esd干啥

因OTP产品都是为了方便客户能修改应用,所以我们都把VPP的PAD都封装出来了;而且在不做VPP功能的时候,我们还加载了其他的IO口的功能在这个脚上;你看现在的MCU都是这么设计的;所以我们需要关心这个脚的ESD的问题!

放个电路示意图看看

现在测试ESD发现这个脚对VDD的+电压特性不好,应该是说当这个加上比VDD高的电压时候的特性不好!

因为这个pad 的工作电压比芯片的VDD高,不能用有PMOS的IO,所以,ESD測試時,對VDD打正電壓的保護能力會比較弱。改善辦法是在layout時把這個VPP垫放在芯片的VCC pad 旁边,可以改善对VDD打正电压时的ESD效能。

还有其他的需要注意的吗?