ESD保护电路

求大侠指点啊!

三言两语怎能解释清楚呢?我也是菜鸟,强烈建议小编好好研究一下GGNMOS的ESD防护原理,这3张图都涉及到它,或者是此基础上栅上加了RC触发电路或其他的触发电路。小编可以看看柯明道中文的那本ESD书,入门够用了。

知道的不多,仅供参考哈~~

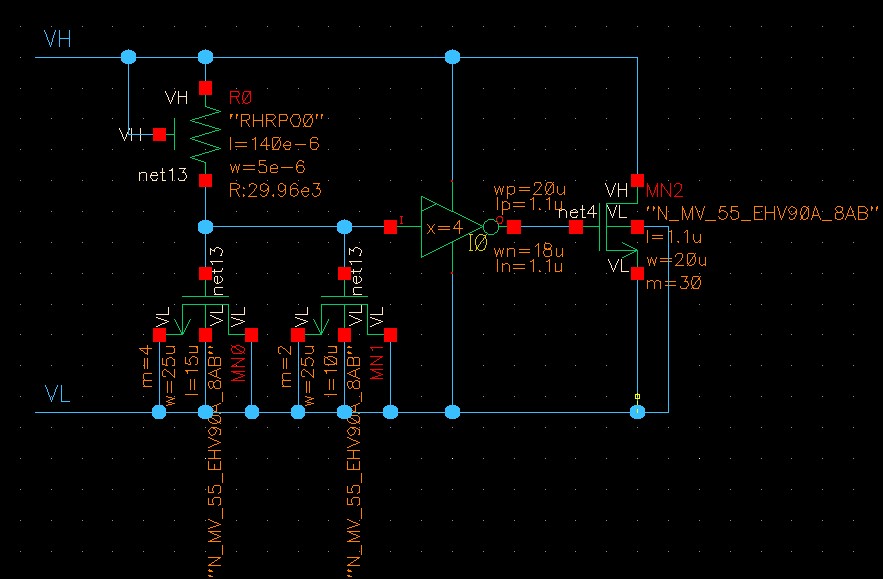

第一幅图:这个应该是电源对地的ESD,当电源VH上有瞬间高压脉冲时,利用RC低通滤波器的特性,电容上的电压不能突变,这样反相器输出高电平,把后面的NMOS管打开,提供ESD电流泄放通路,保护芯片内部的电路。

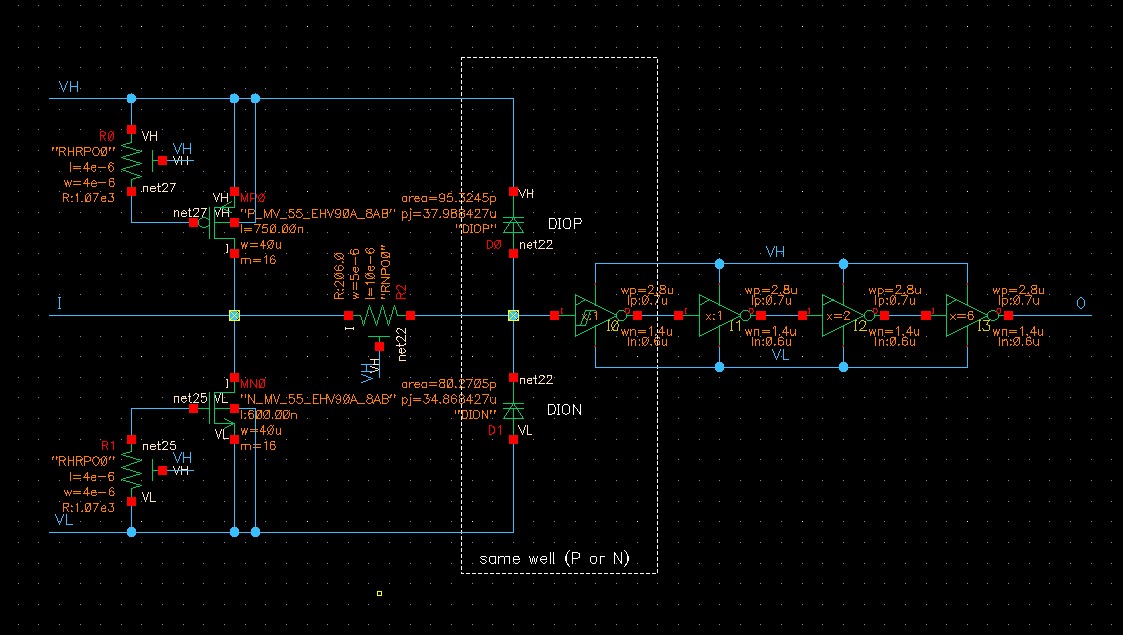

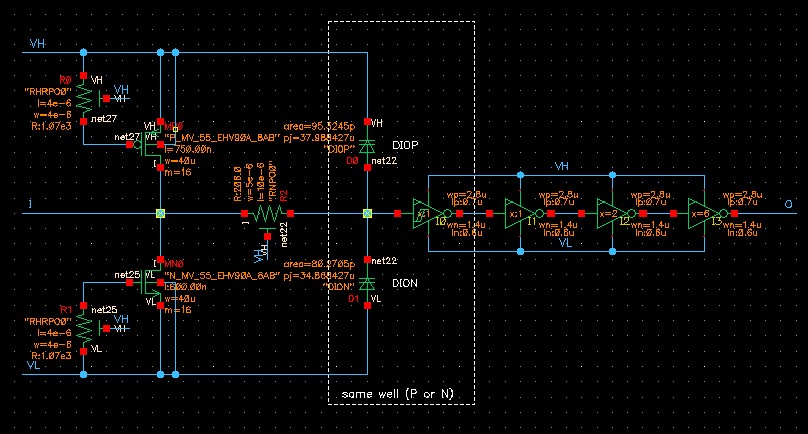

第二幅图:包含了输入端口和输出端口的ESD电路。先说输入的,当输入端口对地打负的ESD时,利用了栅耦合技术,利用输入PMOS管自身的CGD把自己耦合开,提供ESD电流泄放通路;不过这种方法有缺陷,就是有可能耦合瞬间不是所有的finger都能打开,这样电流就集中在某一个或者几个finger上,把MOS管烧坏(灯丝效应)。对电源打正的ESD时利用PMOS管的体二极管提供通路:同理对地打正或者负也是一样的原理

后面的电子和二极管构成了二级ESD保护。

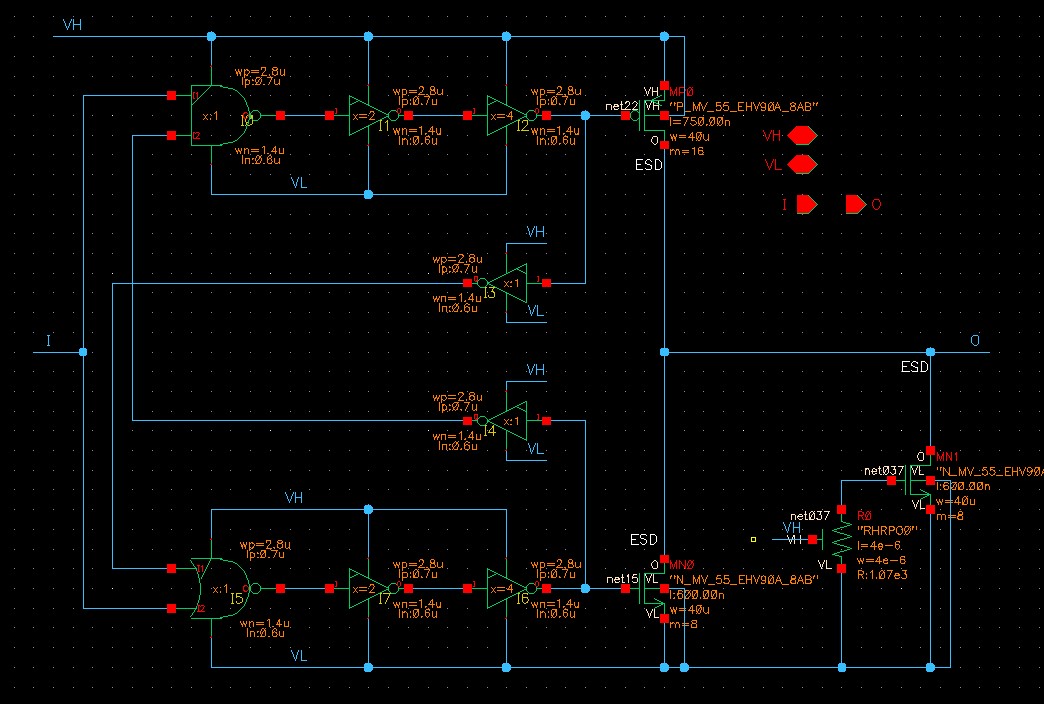

输出的ESD电路其实也是一样的道理,看lz的电路图输出是半桥驱动电路,理论上只要输出POWER MOS足够大,就可以不用ESD,像很多DC-DC芯片中的SW端口一样。在打ESD时可以借用电源VIN到地的ESD。

也在关注中

大哥,你怎么看出来是半桥驱动的,我只看出来是4个反向器串联。貌似不是4个二极管。本人拙见,请大神们指正。

明显不是4个inv,第一个是施密特触发器

谢谢啦,我是需要做这些电路的版图设计,原理还是不很清晰!

很感谢!明白了一些!

第一种适用于频率低的信号,一般我们是采用的第二种方法。由于栅漏间寄生电容的存在,ESD瞬态正电压加在PAD上时, NMOS上的栅极也会耦合一个瞬态正电压,因此NMOS上的每一个“手指”会一齐导通,不用到达Vt1就能进入寄生横向晶体管骤回崩溃区(snapback region)。栅极电压由 Rgate放电到地。这个瞬态电压持续的时间由栅漏寄生电容和栅地电阻组成的RC时间常数决定。栅地电阻必须足够大,保证在电路正常工作时这个栅极耦合NMOS管是关闭的。

研究下

我又有点犯贱了,看见别人说的,我就想说两句,让我自己来说,却又说不好。

个人觉得,这三个ESD保护电路有不同的用途,首先,第一个rc触发确实要考虑频率,但是小编用这种保护电路是用于直流电源和地之间的,即power clamp。其次,第二幅图,是一种两级保护,一般用于输入电路。最后,第三幅图是用于输出电路,我问过我们的博士为什么只用了一个NMOS到vss的ESD保护,博士把我喷了,对我说“看书吧”,没给我解释,个人认为,有两种原因。1.上边PMOS尺寸大,有一定的自保护能力。处于这种考虑,PMOS的设计要考虑ESD性能。2.通过power clamp和下边的NMOS的ESD保护电路共同起作用来实现。个人偏向于后边的解释。因为第一幅图的的rc触发的power clamp如果效率足够强大,是可以只要下边NMOS保护电路。

3幅图有不同的用途。至于小编说要怎样画版图。还是希望小编看书吧。想要真正搞ESD就要自己学习。

小弟也是初学者,希望能得到大神的指正。

你说的还真是,我做的是一款ROMC芯片,第一幅图是该芯片power的保护电路,第二幅是该芯片的输入保护,第三幅是输出保护。但我就是不知道它是如何保护的!

我只总体说一下,这属于ESD的公司机密

这里面除了 常规的GGNMOS 保护之外,还有二级保护,就是除了GGMOS以外, 宽长比很大的管子(我公司有2种接法,分别是BUFFER,SWITCH(也就是TG门)。

这些都叫ESD电路,由GGNOMS(对外合对内放电2种模式) ESD电阻 二级ESD电路组成。这些都属于大公司ESD部门去做,跟版图没多大关系。知道了对版图也没多大作用,跟我公司的大差不差。

很感谢!明白了一些

这个好基础呀,我还是太菜了

图1 4楼已经把原理讲了,这种esd电路的Vt1比GGNMOS低一些,可以通过调整前面的rc控制放电的时间和Vt1,Layout的时候把重点放在后面的nmos上面,这个nnmos要follow foundry的rule,同时注意金属线宽,这个esd电路在布局的时候比较随意一些,因为这个esd的导通均匀性比ggnmos好

图2 这是一个带有二级保护的esd电路,其实对于输入端而言用gcmos加一个隔离电阻足以进行HBM的esd防护,但是你们的designer加入二级保护,个人认为主要用于对CDM模式下的esd防护,所以图中标明两个diode要和后面的inverter的放在同一个well里面

图3 输出端只挂了一个GCNMOS,同时看到图中表明输出p/nmos要做成esd管,nmos有snapback特性,所以导通均匀性差,那么你们的designer比较保守,通过在后面挂一个gcnmos来保护输出nmos,但是pmos因为没有snapback特性,所以pmos自身具有一定的esd防护能力

其实小编的designer在esd方面也是很有功力的,这么好的机会好好把握

拙见而已,欢迎指正,谢谢

kkkkk

刚刚培训过 不过全忘了

three types of circuits.

1> between vdd and gnd, time based RC clamp circuit

2> input pad

3> output driver with non-overlap pre driver

all the gnd connected MOS will serve mainly using the body diode, with the drain

to gate distance longer than normal

哥们,你是南大的?

第一个是vdd到gnd 的clamp电路,设计关键是rc的时间常数,如果芯片面积大的话就需要多个均匀放置,

这里有个whole chip ESD 设计的考虑。

输入ESD是比较常规的了

输出ESD只用了NMOS,这个估计是考虑通过clamp电路实现到地的通路,或者他的输出PMOS足够大了。

结构蛮常见的。

学习中

受教了,謝謝

学习了

Tnany you!

这个esd的电路不要自己画

尺寸要求很严格的

要用工艺厂提供的

abcdefg

efefefefefefefffffffffffffffffffffffeeeeee