请教各位大侠:在pad bonding时,下面哪种版图的画法会减小对pad下面电路的影响

时间:10-02

整理:3721RD

点击:

请教各位大侠:在pad bonding时,下面哪种版图的画法会减小对pad下面电路的影响(如果从应力等方面考虑):

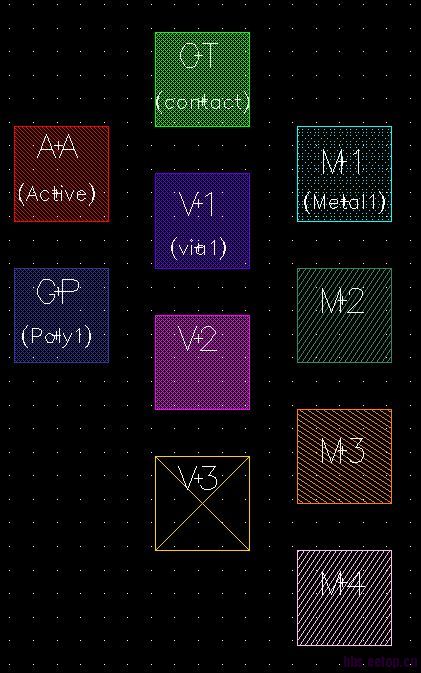

第一种画法:pad直接接到pmos和nmos的漏端。poly1以上没有其他层次覆盖,没有metal的支撑,直接接top metal(metal4)

第二种画法:pad先接到“回”字形的metal3,然后通过metal3接到pmos和nmos的漏端。想用metal3来做支撑,但metal3跨过了poly1

第三种画法:pad先接到覆盖整个mos管区的metal3,然后通过metal3接到pmos和nmos的漏端。用大面积metal3支撑,但metal3完全覆盖了poly1

用线连接到附近空的地方然后用不同的layer包围,再top metal---TEST PAD;不要直接在器件上

谢谢你的指导啊!

但是,就是因为想减小芯片的面积,所以会做PAD on circuit。

实测良率的,理论上,不同的机台、不同的封装形式、打不同的线,结果都不一样,这个只有要封装厂给你评估以及自己做量产测试。

谢谢指导啊!

还是最好不要在PAD下放电路吧~感觉出事是概率问题。

第一点:你要考虑PAD下面要多加metal,这样应力比较好。

第二点:要是esd保护电路放在PAD下面,cont via 处理一定要小心,不然不均匀会挂掉

第三点:esd 放在PAD下面的出事概率是比较大的

谢谢啦!

谢谢啦!

pad只用一层金属,自身接触的可靠性就会差一些。电路周围最好再填充些金属吧。pad对电路的影响不仅是应力方面。跟电路功能有很大关系。

您说的"电路周围最好再填充些金属吧。”

具体是指在哪个周围?

是整个pad top metal的周围?

还是?

当然可以把电路做在padwindow下面,像TSMC的一些工艺就可以这么干,而且他经常这么干,良率完全可以保证。具体怎么画还是要看工艺的,先问清楚工艺的人

谢谢!

foundry 都会提供CUP的design rule。可以参考这种rule的

很多fab都可以的,我就做过TSMC,UMC的esd保护电路放在pad下面的,良率可以,只要做的好,esd达到8kv都没有问题的

我们用的是smic 0.18um的工艺,没有你说的cup的design rule,你可以提供一下相关的design rule吗?

谢谢!

谢谢!