新手版图问题求助~

时间:10-02

整理:3721RD

点击:

各位eetop的大神,小弟刚毕业从事IC设计,版图遇到各种问题,求解。

工艺库用的是IBM bicoms .18的工艺,跑DRC遇到下面问题不知道怎么解决。

1,(RX P+Junction to RX NW Contact) within NW for no latchup <= 53.0 um.

2,PC that intersects RX must have a PC area <= 320.00 sq.um.

3,V1 must be within MT >= 0.00 um.

4,Gates (not over TG) (NOT covered by GRLOGIC) OR Gates (under QT MIM capacitor)must have a RX tiedown by M1 metal.

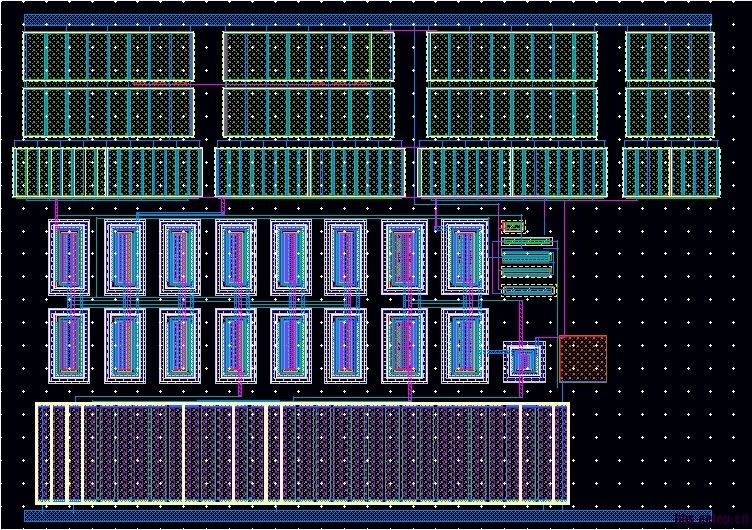

如果版图布局有好意见的也麻烦各位大神指导一下~

工艺库用的是IBM bicoms .18的工艺,跑DRC遇到下面问题不知道怎么解决。

1,(RX P+Junction to RX NW Contact) within NW for no latchup <= 53.0 um.

2,PC that intersects RX must have a PC area <= 320.00 sq.um.

3,V1 must be within MT >= 0.00 um.

4,Gates (not over TG) (NOT covered by GRLOGIC) OR Gates (under QT MIM capacitor)must have a RX tiedown by M1 metal.

如果版图布局有好意见的也麻烦各位大神指导一下~

版图布局

找你身边的同事debug吧,别人也只是猜一下,毕竟没有你们的design rule文件,看着费劲啊

你的layout 上面 gardring 太少了吧,所以drc 会报 关于latch up的错。

1,(RX P+Junction to RX NW Contact) within NW for no latchup <= 53.0 um.

PICKUP 離太遠BODY cont 離太遠

2,PC that intersects RX must have a PC area <= 320.00 sq.um.

PC 面積 太大

3,V1 must be within MT >= 0.00 um.

V1 需要有 MT

4,Gates (not over TG) (NOT covered by GRLOGIC) OR Gates (under QT MIM capacitor)must

have a RX tiedown by M1 metal

可能是 Gates 沒連到 M1

沒有 design rule 只能憑經驗猜一猜

谢谢哦