请教下面逻辑的实现

output [127:0] out

out是一个onehot信号,为1的那位表示in里面从低到高第二个1的位置(注意是第二个。

。。)

比如in == 128'b....10010100

那么out = 128'b000000010000

有什么timing比较好的思路吗?

注意要一拍完成,而且timing要好

我想到的一个思路

就是out每一位为1的条件是

in的这一位为1且

in里面比该位低的所有位是onehot的

out[0] = 0

out[1] = onehot1(in[0]) && in[1]

out[2] = onehot2(in[1:0]) && in[2]

...

out[n] = onehotn(in[n-1:0) && in[n]

不过上面的onehot实现起来也很复杂。。。

比如onehotn(input [n-1] a) =

a ==n'b00...1 ||

a ==n'b00..10 ||

a ==n'b00.100 ||

...

a ==n'b100000;

你这就有点像casex

有周期限制吗?

可以考虑先把0全挤掉做一个中间寄存器,不过这种找1的做法用来找这个1太大材小用了

相当于128个entry带age的arbitration, 2 winner,

4 stage: 4x4x4x2

每个stage选出两个winner

由于vector只有1bit,目测逻辑层数应该可以控制在30以内

这种面试题,出现起码有10年了。

碰到这种恶心题,终极解决方案就是查表

不太明白

能写个伪代码吗?

看起来有点问题

就是如果两个1出现在不同的stage里面怎么办呢

第一个1的方法可以用in^(in&(in-1)),第二个可以去掉最低位1(in&(in-1))在算

128拆分16个8bit分别用这方法算,结果再与上低的所有8bit全0的条件,速度不够pipeline

说实话我觉得你的方法挺好的了,基本相当于casex了,比我想到的方法好

需要这个电路最可能的地方是CAM风格的处理器寄存器重命名电路,而且应该是4发射级别

才需要。如果是这个场景的话,我觉得单周期怎么做都会太慢,对频率的影响过大。

一种取舍方式是把128bit分成2个64bit,对每个64bit算leading one和trailing one。这

样会导致一些限制,可以在发射队列做一些补偿。

另外一种方式是分两个周期来做,也会导致动态范围的降低。

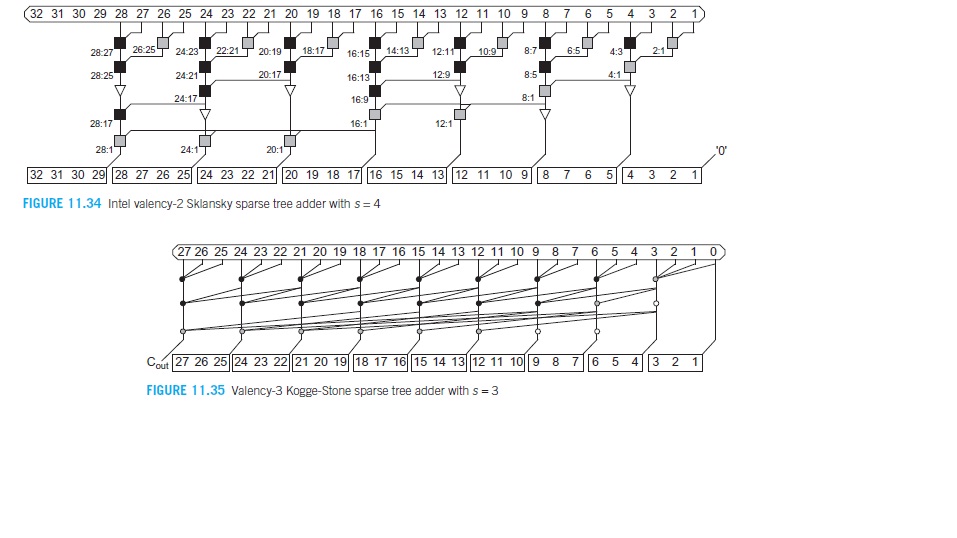

一定要做的话,CMOS VLSI Design 第三版第十章,第四版十一章

数据通路子系统中Parallel-Prefix Computations正好有这个例子,可以参考。

输入A[127: 0],输出Y[127: 0],Z[127: 0]。Y[i]表示从0开始的第一个1的位置,

Z[i]表示从0开始的第二个1的位置。Xij表示Aij一个1也没有,Wij表示Aij只有一个1。

Xii=~Ai

Wii= Ai

Xij=Xik & Xk-1j

Wij=Wik & Xk-1j | Xik & Wk-1j

Yi= Ai & Xi-1:0

Zi= Ai & Wi-1:0

下标混乱,不好意思了。

实现的话,类似加法器的前缀树。

谢谢大牛,请看我下面的注释对不对?

大牛真心不敢当。

是这样的,但也只是解决了一半问题。

另一半是从N多种前缀网络里选一种最合适的。

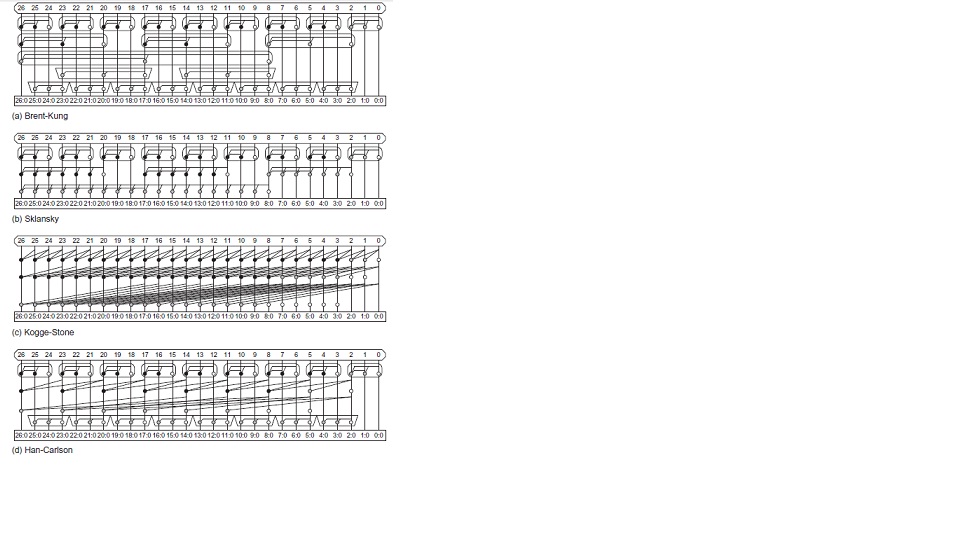

kogge-stone线太多,sklansky扇出太大,brent-kung级数太多。

还有一堆的中间形态。

就是说另外一半问题是如何迭代地算出Wij?

思想是很CLA很像

就是如何算出高位的进位

不过你提到的几种拓扑方法我就不懂了

看了wiki也没看太明白

能不能给简单讲讲具体怎么实现的?

就是说这三种方法各自的思路是什么?

类比加法器的carry tree部分,把Xij类比Pij,把Wij类比Gij,直接替换carry的迭代式

就可以了。

但Wij比Gij逻辑要复杂一点,所以这个电路比相应位数的加法器要慢,考虑到加法器前面

的forward逻辑,后面的MUX,最好的结果也只是有机会和ALU部分速度差不多。

【在 Xaoyao (多帝空魔) 的大作中提到: 】

: 就是说另外一半问题是如何迭代地算出Wij?

: 思想是很CLA很像

: 就是如何算出高位的进位

: ...................

第一张图里面是每一位都计算的,其实我觉得用sparse tree更好一点,现在的工艺条

件,省面积wire的取舍效果更好,经验valency-3可能是最优的(不是特别肯定)。

prefix tree每一层的radix也可以变

比如64位的话,2-3-2-3-2,3-3-3-3可以考虑,128位的话3-3-3-3-2可能比较好?

之所以没考虑用4,我觉得radix-4可能logic effort可能有点高,反而更慢。

这是一道面试题,只要求1个周期做完,没有面积的要求。为什么就没有人想到查找表呢,

1, 128位,8个一组,一共16组,每组对应一个查找表

2, 查找表地址0, 对应于输入0000_0000;查找表地址1,对应于输入0000_0001;。。。

3, 查找表内容包括三个域,第一个域表示,8位输入里面有几个1(大于2个用2表示);第二个域表示,第一个1的位置;第三个域表是,第二个1的位置

比如: 0000_0000 ===> 0, xxxx, xxxxxxx

0000_0001 ===> 1, 0000_0001, xxxxxxx

0000_0010 ===> 1, 0000_0010, xxxxxxx

0000_0011 ===> 2, 0000_0001, 0000_0010

4, 该查找表用寄存器实现。不用rom/ram的原因是,不用delay一拍得到查找结果。

5, 最后,每组写这么一个case。

如果前面的组没有1,并且本组有2个1,那么本组输出第三个域

如果前面的组只有1个1,并且本组有1,那么本组输出第二个域

其他情况,本组输出0