PLL中的CML/CMOS逻辑转换电路

时间:12-12

整理:3721RD

点击:

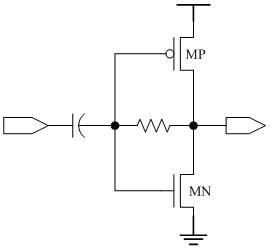

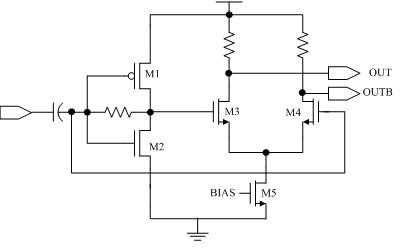

附件是PLL中cml和数字CMOS间的逻辑转换电路,分别为CML-TO-CMOS Converter和CMOS-TO-CML Converter,请问二者在设计时需要注意哪些?

在目前的设计中,放到系统中,感觉噪声很大,功耗也很大(200多uA),感觉应该是设计不够合理.请问哪位大侠给些指点?或有相关的paper推荐一下,谢谢!

在目前的设计中,放到系统中,感觉噪声很大,功耗也很大(200多uA),感觉应该是设计不够合理.请问哪位大侠给些指点?或有相关的paper推荐一下,谢谢!

第一种最好先进行差分到单端的转换,AC couple要注意信号带宽和信号幅度的寄生损耗。

第二种没有必要,CMOS可以直接驱动CML。

谢谢回复!

第一种:“先进行差分到单端”有什么好处吗?

第二种:CMOS是单端,CML是双端,是否还需要一个单端至双端的转换?

有没有相关的推荐paper?

再次感谢!

先进行差分到单端可以抑制信号共模噪声

一般CMOS是单端,可以简单的延时匹配到CML双端。或者用CVSL电路(就是类似Level Shift)转差分驱动CML。

第一种的电阻反馈构成了高通,工作频率不能太低。