MOS和diode漏电流的仿真正确吗(更新,节点电流也不为零了)

时间:12-12

整理:3721RD

点击:

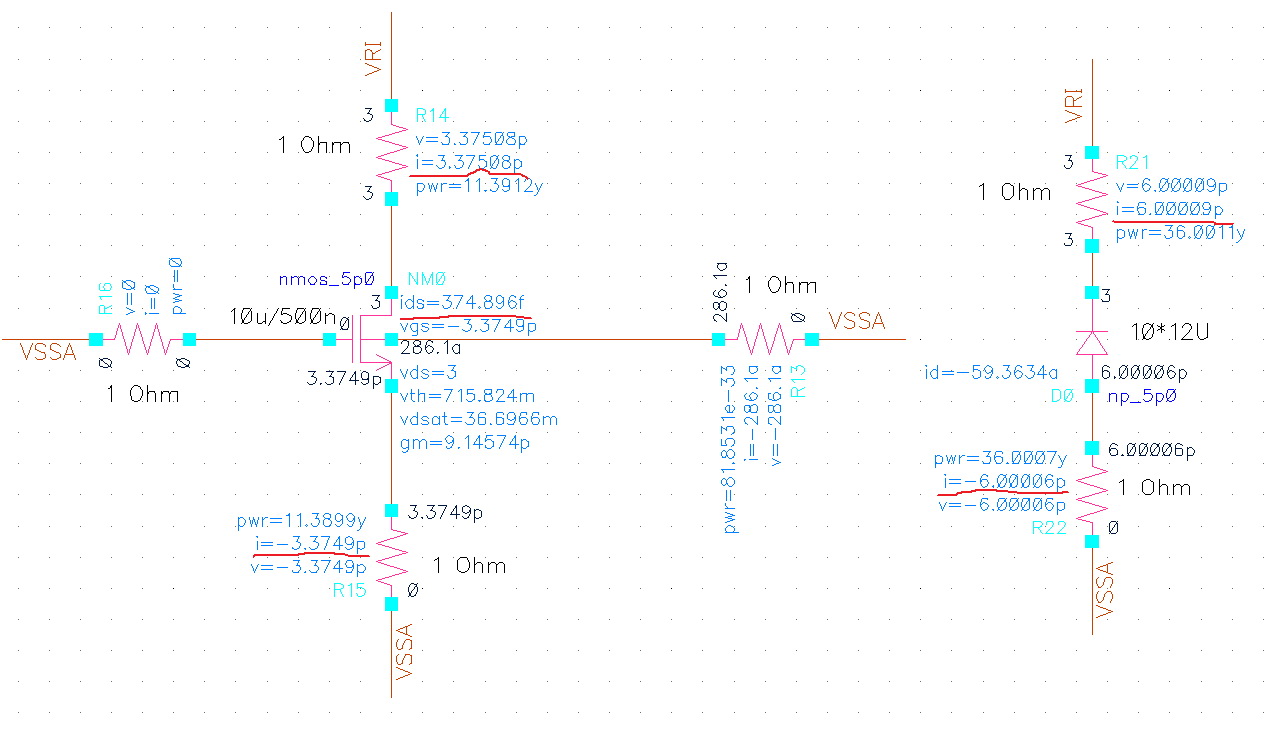

想看看MOS开关和二极管的漏电流,搭了个电路仿真了一下。

四个角都接的1欧姆的电阻(为了方便看电流)。

如图,从电阻看起来漏电流是3p和6p,但从mos和diode本身的

参数看起来却是ids=374f和id=59a。

不知哪个正确,还是不能用这个模型仿真。谢谢!

四个角都接的1欧姆的电阻(为了方便看电流)。

如图,从电阻看起来漏电流是3p和6p,但从mos和diode本身的

参数看起来却是ids=374f和id=59a。

不知哪个正确,还是不能用这个模型仿真。谢谢!

用的理想电阻吗?

看电流可以用0V Vdc啊。再试试。

还有source和bulk的通路,可能是d-b-s流的,所以ids看不到。

仔细仿真了一下,节点总电流也不为零了,如图所示(图要点一下)。

应该不是仿真误差的问题,电流的容忍误差已经调到1pA甚至更低了。

不知是不是有些潜在通路。

二极管漏电流那个也有节点总电流不为零的情况。

我觉得这种精度下,spice仿真器的结果都不可信了

KCL肯定是要遵守的,那个是所有电路解的基石之一

漏电一直都是不可仿,至少我接触过的模型都不可以,就算有,也别信

pA是什么,pA是nothing啊,nothing=nothing,应该算正常吧

这个应该是仿真的问题,就是上面仁兄说的,KCL必须要遵守。

可以修改gmin参数提高仿真精度,建议至少提高2个数量级。

高!spectre 自动加了1000G电阻到浮空节点,导致误差。