请教:为何pipeline中的SHA的SDDR随输入信号有明显的下降?

时间:12-12

整理:3721RD

点击:

做了个14bit,100MHZ的pipeline的SHA,采样频率100MHz,当输入信号频率为10MHz时,

SNDR=99.8db当输入信号频率为30MHz时,SNDR=83.5db,当输入信号频率为49MHz时,

SNDR=76.5db

请教高手解答如何解决这个问题

SNDR=99.8db当输入信号频率为30MHz时,SNDR=83.5db,当输入信号频率为49MHz时,

SNDR=76.5db

请教高手解答如何解决这个问题

可能是运放的带宽不够,也可能是开关的线性度不够

问一下,你用的是哪种架构?Flip-Around or Charge-Redistribution

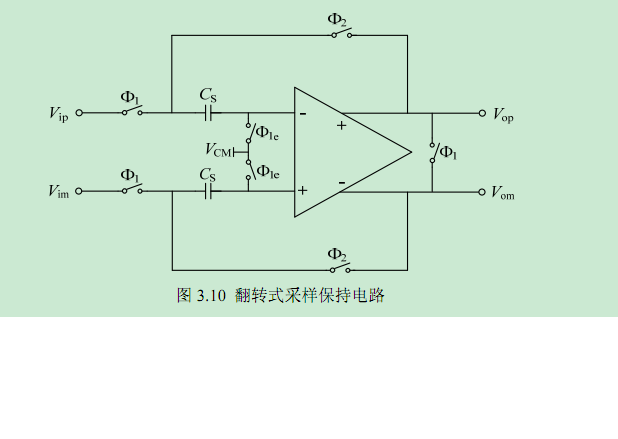

采用的是翻转式采样保持电路,运放的GBW=1.12gHZ 开关的线性度还没测,现在测试下看

看。谢谢了

这个14bit可以sim出来。

但是能做得出来吗?实际能有12bit吗?

现在工艺能做得了吗?

找到问题了 是连接clock1e的那个开关太小了,现在改为1000um/0.18um 后sndr=97db

但是感觉这个开关太大了?

请教!

仿真定的,从100放到了3000um 就1000um最好

是不是有问题啊?

请教!

仿真定的,从100放到了3000um 就1000um最好

是不是有问题啊?

请教!

兄弟,你不会用bootstrap来提高开关的线性啊。这么大的mos管?

采用的SHA结构如图所示 在输入信号路径上的是采用bootstrape开关,和vcm1相连的开关

采用的是1000um/0.18um的NMOS,这个是不是证明我的bootstrape的线性度不够啊?

谢谢啦!

booststrape多大,也是这么大?可以用理想开关代替掉与vcm相连的两个开关测一下,这两个开关注入也有影响的,在运放输入正负端再接一个辅助开关也可能有助于改善采样精度。