高手来讨论下,这是测试环境的问题还是IC本身的问题

时间:12-12

整理:3721RD

点击:

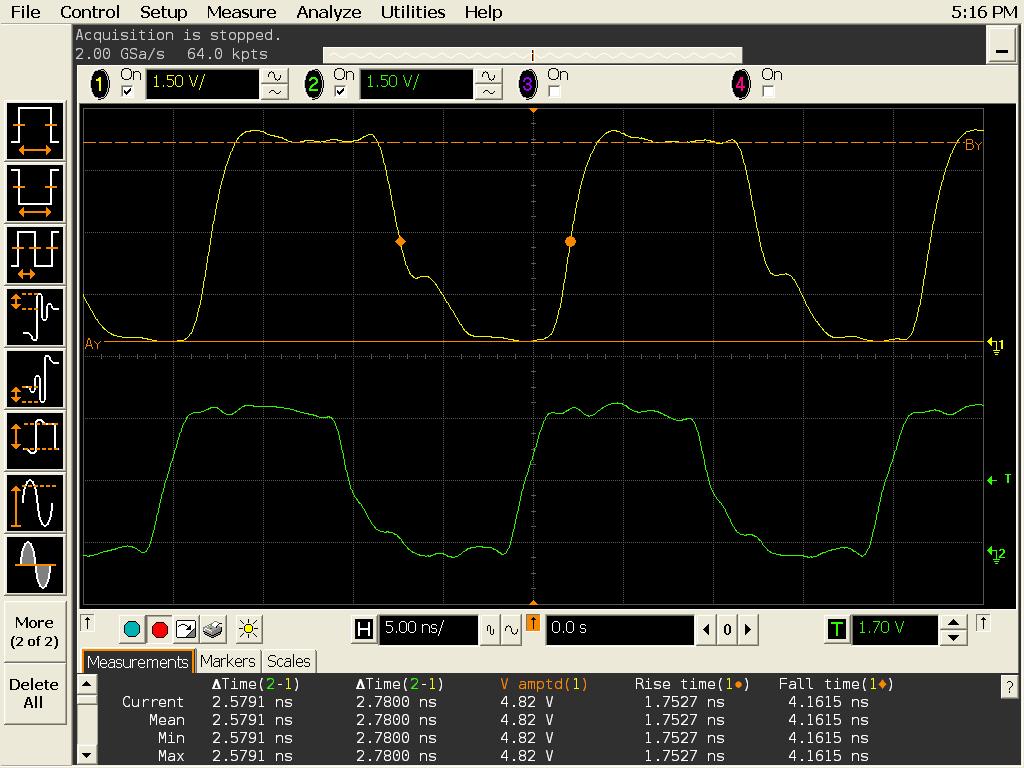

如附件所示,下面是输入波型,上面是输出,50M的Clock。请关注输出下降沿的kink,我原先的理解是这个由寄生的电感引起。

但是第一个奇怪的是上升沿没有而只有下降沿有,这点和仿真加入寄生电感的情况不符。上升和下降沿的驱动能力测试过是差不多的。

第二个是,这个东东和方波的频率有关,随着频率的上升越来越明显,在较低频率下,比如30M以下,这个东西就没有了。我不理解在Tr,Tf没有明显不同的情况下,为什么会和频率有关?

请高手指点一下。

但是第一个奇怪的是上升沿没有而只有下降沿有,这点和仿真加入寄生电感的情况不符。上升和下降沿的驱动能力测试过是差不多的。

第二个是,这个东东和方波的频率有关,随着频率的上升越来越明显,在较低频率下,比如30M以下,这个东西就没有了。我不理解在Tr,Tf没有明显不同的情况下,为什么会和频率有关?

请高手指点一下。

看起来是因为信号完整性的关系,所以上升/下降会有些不一样,但是又和频率相关

简单说就是电磁波在金属线里弹来弹去,而线阻抗什么的和频率相关,

你去google下信号完整性,很容易找到些入门简介什么的看了就明白了

可能是输出transistor的miller effect...

贴一下输出级的电路看看...

输出就是很普通的上一个PMOS下一个NMOS,分别由一个NOR和一个NAND控制,有一个enable信号。

你跑下GPIO的仿真,看看PMOS和NMOS的gate端的波形,关注下下降时候,看看这2个

波形有没有交叉。

你描述的nor+nand+pmos+nmos+enable啊,就是输出的I/O。

你可以试试看,输入50MHz,输出接10pf loading,

然后变化下频率和loading,多跑几次仿真比较下。

你的nand/nor是不是用小尺寸器件,那个时候电流不够discharge那个mosfet...

单独仿仿那个输出级看看...