flip-flop的亚稳态特性是什么意思?

时间:12-11

整理:3721RD

点击:

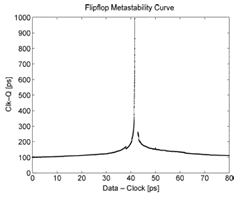

看到论文里有附件这张图,具体什么意思?怎么用Hspice进行仿真?

锁存器是不是也有类似的特性?

thx

锁存器是不是也有类似的特性?

thx

应该是这样,

如果时钟的锁存发生在输入数据变化的不恰当时期,即输入电平

刚好使flip-flop处于亚稳态,则flip-flop需要一定的时间来

分辨,进入0或1(因为处于压稳态,最终到0或1是不确定的)

所以在某一点有一个尖峰,使得clock到输出时间激增,这就是亚

稳态分辨所需要的时间。

仿真不知道怎么仿才好,因为我不知道怎么扫描clk的时钟边沿。

一个笨办法是,对于输入的斜坡,不断调整clk边沿的位置,计算

clk-q数据,自己再画图。

我一直很怀疑Hspice是不是能仿真出“不确定是0还是1”的情况

毕竟spice的基础是解微分方程,输入是一定的话,输出也是一定的