DC综合里加了门控时钟,综合后仿真出错

时间:10-02

整理:3721RD

点击:

RTL里没有加门控,在DC脚本里加了insert_clock_gating插入锁存器+与门的门控,综合后FORMALITY验证通过,结果后仿时,用的testbench和没加门控时的后仿代码相同,结果却不对,请问是为什么?怎么解决?门控的使能信号是内部产生的,也不理解,求赐教~谢谢

如果是DC自己插入的clock gating,那基本没啥问题。后仿出问题再正常不过了,一般都是timing问题,抓信号分析就好了,TB在port上记得也最好要加delay。

空说无凭,要想证明是clock gating的问题,请先抓出出问题的地方的波形。

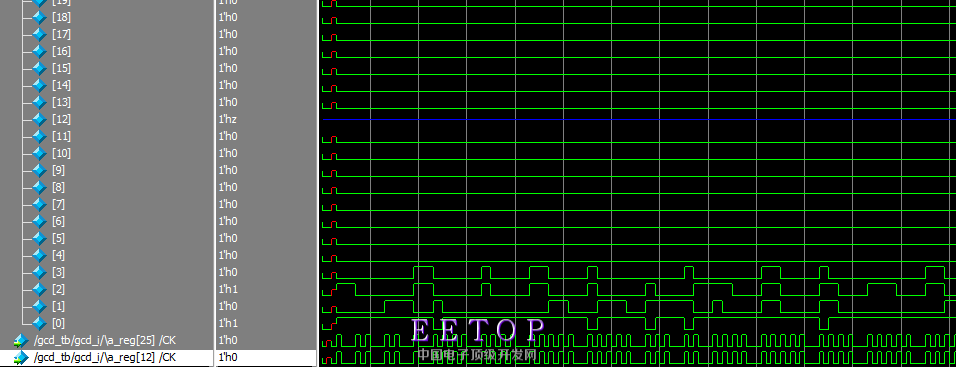

谢谢回答,抓波形看了一下,模块内有些寄存器在异步复位后变成了高阻态,是我插门控出错了吗?用的set_clock_gating_style和insert_clock_gating两条语句,谢谢!

这些寄存器用的时钟是不是有一段高电平

没有,始终是高阻态

你的意思是这些寄存器的clk端就是高阻,就是clock gate的输出是高阻?

如果该时钟默认是高电平, 即我们平时说的反相时钟, 那么插入的CG 输出的时钟为不定态, 需要在这里deposit一个值。

不好意思我不太明白,能不能详细说一下?

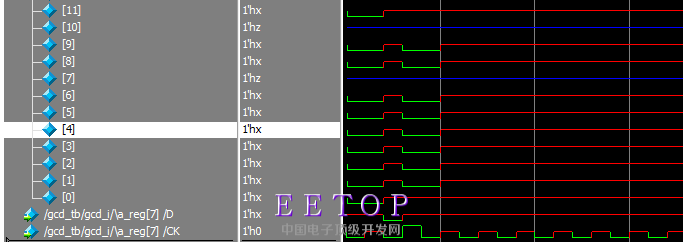

我看到gck_tb/gci_i/\a_reg[12]/ck是有时钟的,这个时钟clock gate模块的输出还是输入

是输入的门控时钟,上面蓝色是它的数据输出

你的意思ck是clock gate模块的输入时钟,蓝线是clock gate模块gate后的输出时钟

那使能信号是z态吗

ck是电路中某个工作用寄存器的输入时钟,来自clock gate的输出,蓝线是这个工作寄存器的输出

那这个寄存器的输入呢,如果是z就对了,

如果不是,就是说一个寄存器,时钟正确,输入数据正常,但输出是个高阻?

咱们还是先说第一幅图,你是说a[12]的输入也是z,那我们就要沿着这个z往前找,看是谁输出的它