关于异步复位、同步释放的问题

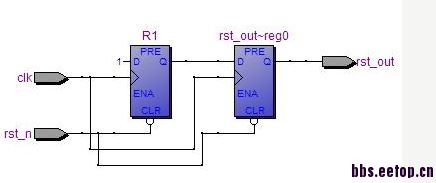

这个电路图的原理我懂,就是rst_n的“1”打2拍来同步输出,用两级同步器是为了消除第一级同步器的亚稳态。但我认为两个同步器都是异步复位,复位信号与时钟都是连在一起的,在第一个同步器出现亚稳态时,第二个同步器也会出现亚稳态的问题,这样给后面的电路的复位会造成影响,没能很好的解决亚稳态的问题。我倒觉得把第二级同步器的复位信号给去掉更好点,只给第一级复位信号。小弟纠结好久了,可能小弟哪里理解错了,求各位大神指点。

这个电路图的原理我懂,就是rst_n的“1”打2拍来同步输出,用两级同步器是为了消除第一级同步器的亚稳态。但我认为两个同步器都是异步复位,复位信号与时钟都是连在一起的,在第一个同步器出现亚稳态时,第二个同步器也会出现亚稳态的问题,这样给后面的电路的复位会造成影响,没能很好的解决亚稳态的问题。我倒觉得把第二级同步器的复位信号给去掉更好点,只给第一级复位信号。小弟纠结好久了,可能小弟哪里理解错了,求各位大神指点。

我理解在解复位到来的第一个时钟周期,第一个触发器由于输入输出不同有可能输出出现亚稳态。第二个触发器在第一个时钟周期是不会出现亚稳态的,因为这时它的输入输出都为0。那么问题来了,第一个触发器的亚稳态会不会传递到第二个触发器呢?是有可能的,但是概率是低到可以容忍的。按照一些资料上提供的公式,第一个触发器的mean time between failure ,MTBF1=C1*e^Tr/(C2*Fclk*Freset), 第二个触发器MTBF2=C1*e^Tr/(C2*Fclk*Fdata1)。有一个计算结果是当MTBF1=40秒,MTBF2=1000年!一千年出一次问题。

打拍可以减少亚稳态传递的概率。我见有些同步复位电路,采用5级打拍,这样基本上保证不会出现亚稳态。

少年你想的太多了。

二楼解释得很好

理论上讲打多少拍都不能解决亚稳态,只是会极大地降低出现概率

1、亚稳态在组合电路里传递很快,但在多级寄存器间传递则越来越小,MTBF也越来越大,因为触发器的输出相对来说稳定得多(这个要看数字电路原理RS触发器的构成,你要知道,RS触发器可以用来做按键消抖),所以经常用多级触发器来打拍,让异步信号同步化。

2、你列出的这个异步复位、同步释放电路里,看清楚哦,只是一个复位电路,它输出的是复位信号,是要输出给别的电路复位端的!不是给自己用的! 这个电路的重点在同步释放,就是复位信号的释放,它的释放,绝对在Tcq之后,紧贴Tcq,所以在下一次时钟沿之前,给复位后的第一个数据留足了setup time,这样有效解决了复位后第一个数据采集的亚稳态问题。

进入复位的时候有亚稳态,进入复位一段时间后以及退出复位时没有亚稳态。在不关心进入复位时的电路功能的应用里,这样做就没有问题。

讲解的非常好!

为啥不弄成同步复位 同步释放呢?

解释的真详细

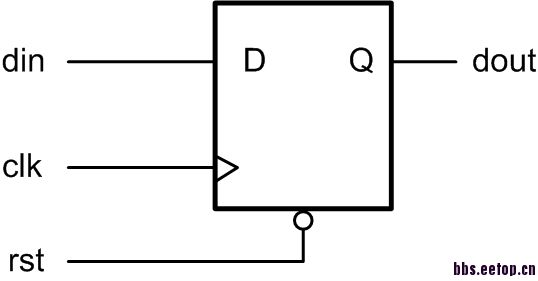

您好,我在一篇文档里看到,说退出复位时也会产生亚稳态,

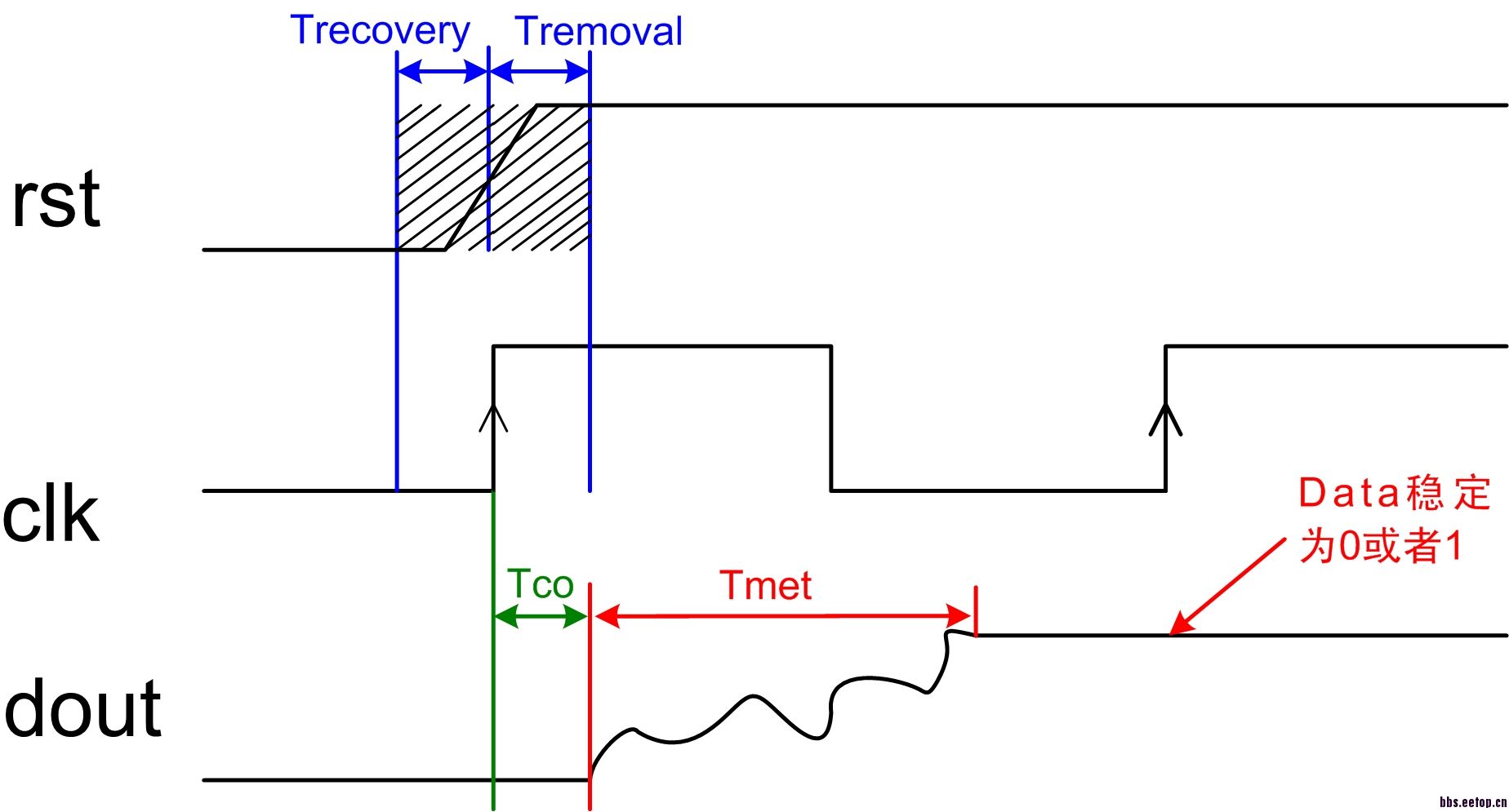

他的解释为“如果异步复位信号的撤销时刻在Trecovery(恢复时间)和Tremoval(移除时间)之内,那势必造成亚稳态的产生,输出在时钟边沿的Tco后会产生振荡,振荡时间为Tmet(决断时间),最终稳定到“0”或者“1”,就会可能造成复位失败。”按照他的说法,复位释放时也会产生亚稳态,不知道哪种说法是对的?

他的解释为“如果异步复位信号的撤销时刻在Trecovery(恢复时间)和Tremoval(移除时间)之内,那势必造成亚稳态的产生,输出在时钟边沿的Tco后会产生振荡,振荡时间为Tmet(决断时间),最终稳定到“0”或者“1”,就会可能造成复位失败。”按照他的说法,复位释放时也会产生亚稳态,不知道哪种说法是对的?

明白人,,,

2楼真解。太感谢了。郁闷了一天和小编一样的问题

我饿的理解是释放的第一拍有可能发生亚稳态,第二拍降低概率。

仔细看看

这个问题非常赞,因为我也纠结了很久

我目前的理解是第二个触发器可以帮助阻止第一个触发器的亚稳态传播,但是无法解决第二个触发器自身的亚稳态传播

这牵扯到一个问题:两个触发器拥有相同的clk和rst信号,一个触发器产生了复位亚稳态,另一个是不是也一定会产生复位亚稳态?

如果答案是YES,那么弄多少个触发器都不会解决最后一个触发器的亚稳态问题,除非它们用不同的rst信号,但这又牵扯到如何同步复位触发器形成系统异步复位的问题。

异步复位产生亚稳态的原因跟异步采样产生的亚稳态原因是不同的:前者在于clk和rst的关系,这跟各个触发器都有关联,每一个触发器都是有机会产生亚稳态问题的;后者在于采样输入数据和clk的关系,这只跟第一个触发器有关联,只有第一个触发器可能会产生亚稳态问题,所以用后面的触发器可以阻止第一个触发器的亚稳态传播。

不知我的理解是否正确,恳求大牛们来解惑啊

#9楼说的是指小编的异步复位 同步释放电路,在释放时不会有亚稳态产生。你所提供的图是异步释放的,可能会有亚稳态产生

我觉得多少级触发器都无法解决异步复位时产生的亚稳态问题,解决方法是复位较长一段时间,如#9楼所说 异步复位同步释放电路,主要是解决同步释放时产生的亚稳态