关于`define的作用域的一些疑问?

时间:10-02

整理:3721RD

点击:

众所周知,`define定义的宏可以实现“跨模块、跨文件、整个工程”的大范围的使用,

这次我用`define定义适用于整个工程的参数,然后单独放在一个.v文件里面。

现在的问题是:

(1)如果想在工程里面所有地方都可以使用这些`define,我发现只能在每一个模块或者源文件里面都用`include命令包含头文件。

想问有没有更简单的办法?

(2)如果没有其他办法,那么在VIVADO源文件管理界面上,会有很多个“头文件”显示出来(取决于我调用了多少次),

对于小模块很多的工程,界面很不美观,然后remove这些头文件肯定也是报错的。

想问有没有至少让这个界面美观一点的办法?

++++++++

谢谢各位!

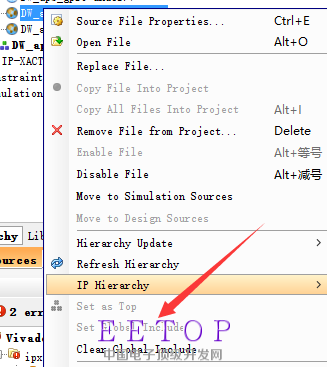

找到要被global define的文件,vivado中鼠标右单击会看到那个选项

这次我用`define定义适用于整个工程的参数,然后单独放在一个.v文件里面。

现在的问题是:

(1)如果想在工程里面所有地方都可以使用这些`define,我发现只能在每一个模块或者源文件里面都用`include命令包含头文件。

想问有没有更简单的办法?

(2)如果没有其他办法,那么在VIVADO源文件管理界面上,会有很多个“头文件”显示出来(取决于我调用了多少次),

对于小模块很多的工程,界面很不美观,然后remove这些头文件肯定也是报错的。

想问有没有至少让这个界面美观一点的办法?

++++++++

谢谢各位!

同问!

我想到的 办法是 可以用一个总的头文件把零散的头文件include即可。 当然大型项目中,可以用几个代表性头文件(按模块或层次) 来include零散头文件。

你说的这个并没有解决我说的问题啊,就算只有一个头文件,那还不是要在每个使用`define的源文件里面都调用一次。

我的使用体会,各家软件对此问题处理不一样。vivado只要把define文件设成global include就可以提供全部文件使用。verdi只要包含define文件就行。vcs则需要指定define文件的目录,并且在文件头上要包含include。

请问Vivado 在中如何将宏文件设置成global include?

找到要被global define的文件,vivado中鼠标右单击会看到那个选项

在综合选项里加上 -verilog_define + 内容 就可以了

TCL建工程可以用 add_files {xxx }-scan_for_include xxx/include/

set_property file_type {Verilog Header} [get_files xxx/include/defines.v]

这个真是极好的

涨姿势了