关于6T SRAM的verilog建模

时间:10-02

整理:3721RD

点击:

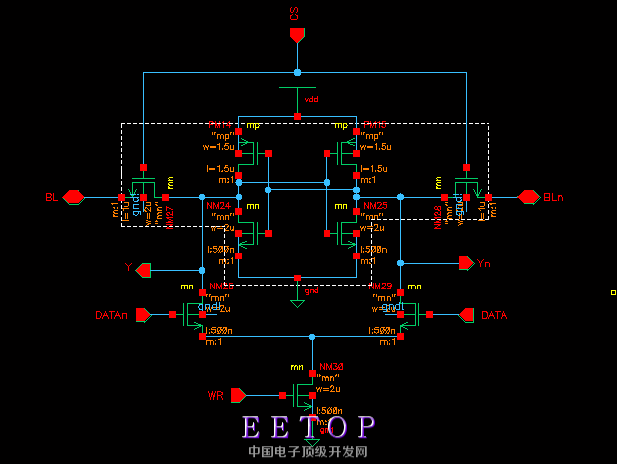

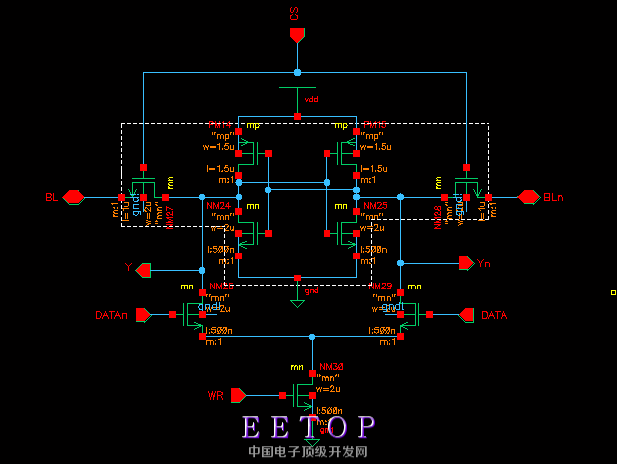

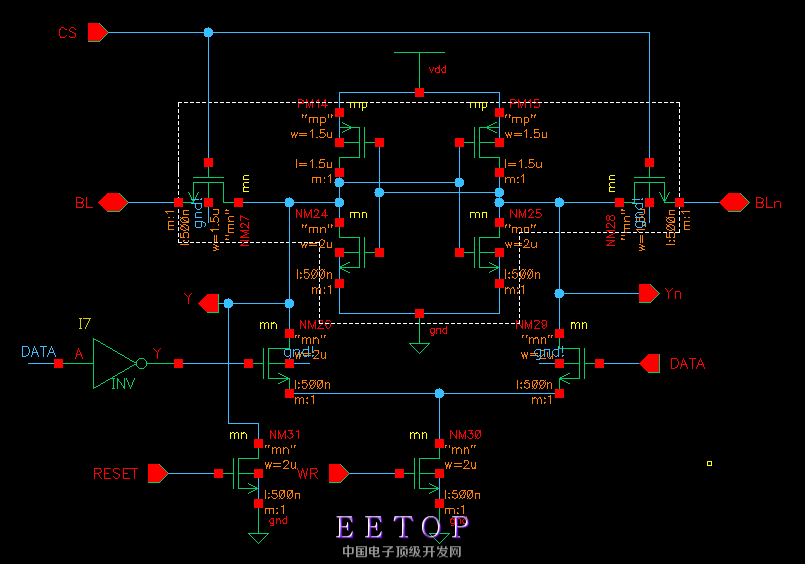

求大师讲讲对特殊SRAM IO的处理:

图中的BL双向口信号怎样去建模呢?用tranif1?

还有下方的WR信号,是用边沿还是电平?若是边沿是上升沿还是下降沿呢?

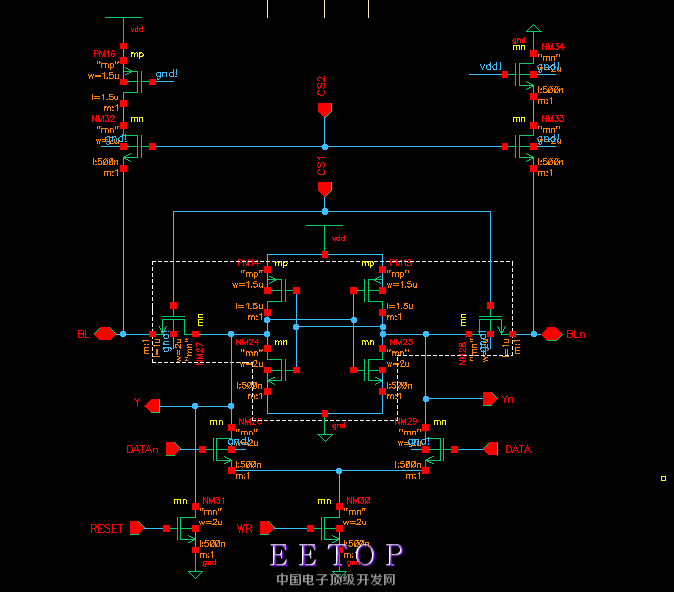

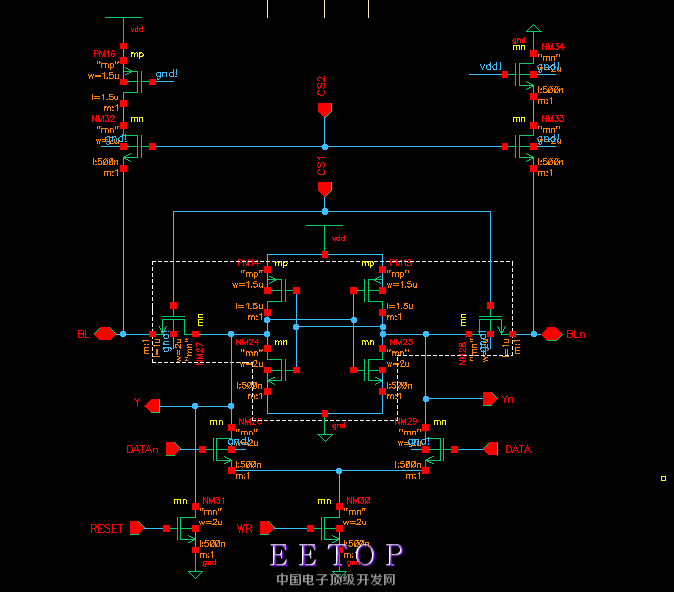

更复杂一点的呢:

希望多多指点

该代码已通过行为仿真

图中的BL双向口信号怎样去建模呢?用tranif1?

还有下方的WR信号,是用边沿还是电平?若是边沿是上升沿还是下降沿呢?

更复杂一点的呢:

希望多多指点

没人光顾,自己顶一下

- module SRAM ( Y, Yn, BL, BLn, CS, DATA, RESET, WR );

- inout BL, BLn;

- input CS, WR, RESET, DATA;

- output Y, Yn;

- reg cache;

- tranif1 u1(BL,Y,CS),

- u2(BLn,Yn,CS);

- buf (weak1,weak0) u3(Y,Y);

- buf (weak1,weak0) u4(Yn,Yn);

- assign Y=cache;

- assign Yn=~cache;

- always@(RESET or WR or CS)

- begin

- if(RESET)

- cache<=0;

- else if(WR==1'b1&&CS==1'b0)

- cache<=DATA;

- else if(CS==1'b1&&WR==1'b0)

- cache<=BL;

- end

- endmodule

该代码已通过行为仿真

感谢小编的无私行为。

谢谢分享!