FPGA的FIFO IP核应用与UDP传输的问题

时间:10-02

整理:3721RD

点击:

AD连续采集的数据(采集频率50MHz以内),经FIFO缓存,通过千兆以太网发送至labview显示,每次发送512个字节。

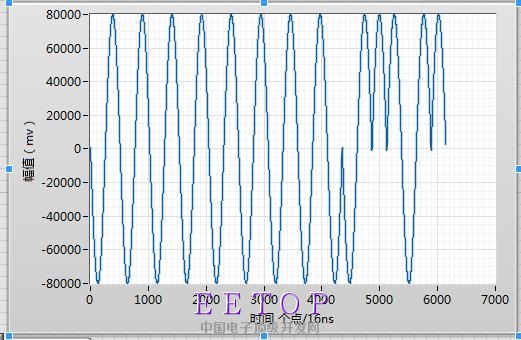

(1)两个FIFO交替缓存,存满FIFO1后才开始传输数据,传速度大于写速度,传完后等待,另一个FIFO2存满再读取,如此循环。理论上FIFO不会溢出。但labview收到数据4K个点后,数据开始错乱。

(2)单写一个FIFO,给它写满后,再传空后,再写,labview上收到的数据也是4K个点是对的,然后开始错。修改FIFO深度也是没影响的。

问题:这FIFO有什么特殊的操作吗?为什么是4K啊?找不到原因。求助大家!ps:signal tapii里观察没有什么问题。

可能溢出了,确定一下到底有没有溢出

理论上分析,先写满fifo1,再写fifo2的同时读取fifo1,读频率高,读空后等待fifo2写满。 signal tapii上现在也看不出溢出了。

之前有看到过,在读使能的时候,只读了fifo里一个数据后就退出了,感觉结果就是有时没正常工作,导致数据溢出,可是为什么呢?

It may be empty then labview stop to read, then wait. But wait too long

在chipscope中看一下FIFO的FULL信号是否有效就知道了。

并没有溢出