verilog中使用task出现的问题

时间:10-02

整理:3721RD

点击:

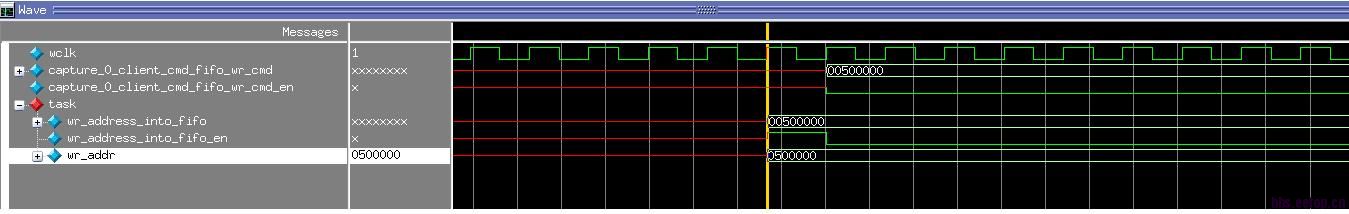

小弟在使用verilog task中出现了一个问题。即在调用存在端口的task时,相应信号对应的波形不一致。即capture_0_client_cmd_fifo_wr_cmd信号和task中的wr_address_into_fifo信号;还有capture_0_client_cmd_fifo_wr_cmd_en信号和task中的wr_address_into_fifo_en信号不一致。波形如下图所示。

代码如下所示:

module task_test;

reg wclk; //74.25M

//wclk

initial

begin

wclk = 1'b0;

forever

begin

#6734;

wclk = ~wclk;

end

end

integer addr0;

integer j0;

reg [29:0] capture_0_client_cmd_fifo_wr_cmd ;

reg capture_0_client_cmd_fifo_wr_cmd_en ;

initial

begin

addr0 = 5242880;

end

task write_BL0; //only write 256 bit data

output [29:0] wr_address_into_fifo;

output wr_address_into_fifo_en;

input [26:0] wr_addr;

begin

#100;

wr_address_into_fifo_en = 1'b1;

wr_address_into_fifo = {3'b0,wr_addr};

@(posedge wclk);

#100;

wr_address_into_fifo_en = 1'b0;

end

endtask

initial

begin

for(j0=0;j0<50;j0=j0+1)

@(posedge wclk);

write_BL0(capture_0_client_cmd_fifo_wr_cmd,capture_0_client_cmd_fifo_wr_cmd_en,addr0[26:0]);

end

integer t;

initial

begin

for(t=0;t<1000;t=t+1)

@(posedge wclk);

$stop;

end

endmodule

代码如下所示:

module task_test;

reg wclk; //74.25M

//wclk

initial

begin

wclk = 1'b0;

forever

begin

#6734;

wclk = ~wclk;

end

end

integer addr0;

integer j0;

reg [29:0] capture_0_client_cmd_fifo_wr_cmd ;

reg capture_0_client_cmd_fifo_wr_cmd_en ;

initial

begin

addr0 = 5242880;

end

task write_BL0; //only write 256 bit data

output [29:0] wr_address_into_fifo;

output wr_address_into_fifo_en;

input [26:0] wr_addr;

begin

#100;

wr_address_into_fifo_en = 1'b1;

wr_address_into_fifo = {3'b0,wr_addr};

@(posedge wclk);

#100;

wr_address_into_fifo_en = 1'b0;

end

endtask

initial

begin

for(j0=0;j0<50;j0=j0+1)

@(posedge wclk);

write_BL0(capture_0_client_cmd_fifo_wr_cmd,capture_0_client_cmd_fifo_wr_cmd_en,addr0[26:0]);

end

integer t;

initial

begin

for(t=0;t<1000;t=t+1)

@(posedge wclk);

$stop;

end

endmodule

波形图

麻烦大牛指点下。

麻烦大牛指点下。

task应该是等你这个任务结束的时候才会将输出值送出去

task write_BL0; //only write 256 bit data

output [29:0] wr_address_into_fifo;

output wr_address_into_fifo_en;

input [26:0] wr_addr;

begin

#100;

wr_address_into_fifo_en = 1'b1;

wr_address_into_fifo = {3'b0,wr_addr};

@(posedge wclk);

#100;

wr_address_into_fifo_en = 1'b0;

end

// 到这里才将output输出出去

endtask

这只是我的理解,我手里没有确切的资料可以有证明是这样

楼上说的很全面了

楼上讲解得对的,非常感谢!

很好,学习学习

原来是这样。

task存在被同时调用的情况吧,而且非automatic的task的参数以及中间变量的内存空间是一样的。

共同吸取经验

如果是全局变量,可实时变化吧,不用output。

正解