GTX example design 好简单 但是我有一个问题。

时间:10-02

整理:3721RD

点击:

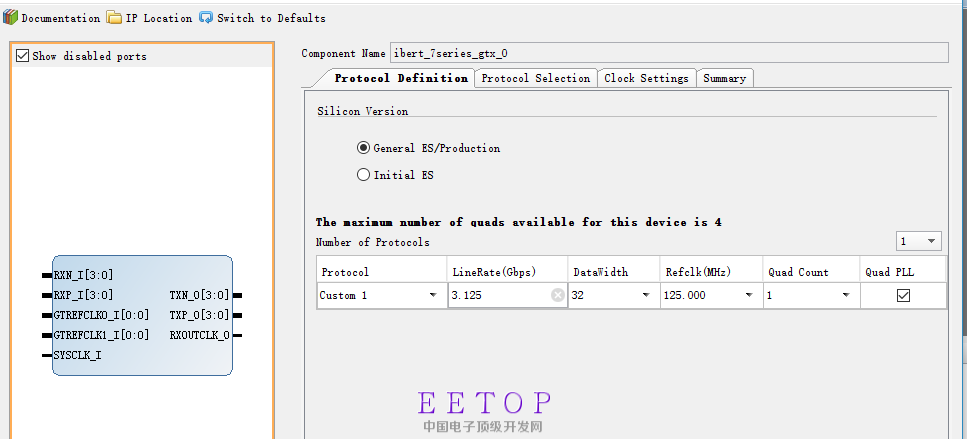

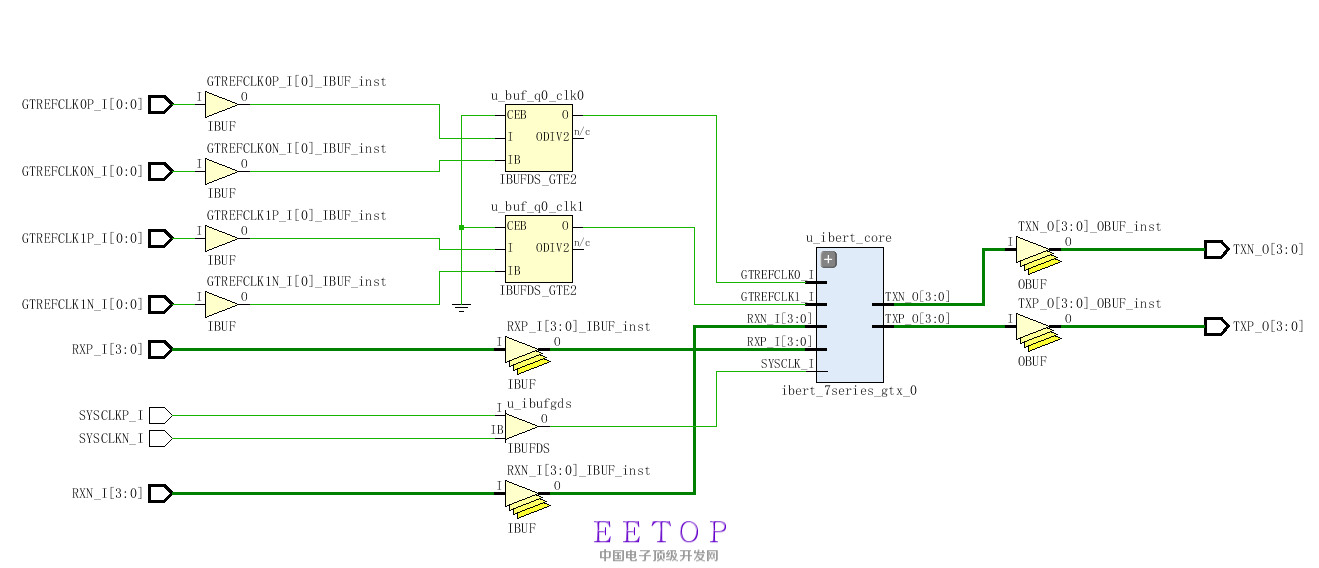

我生成GTX,都是按默设置认来进行的。上图是设置,下图是example design的RTL.

我看文档说,GTX是串并,并串转换器。但是RTL显示并没有。这是怎么回事,如图所示:RXN,RXP都是[3:0],但是TXP,TXN也是[3:0],并串转换是空话吗?

4通道吧

首先谢谢您的回复。

我实际上找错了,这个根本不是GTX,而是IBERT.

IBERT是Xilinx提供用于调试FPGA芯片内高速串行接口比特误码率性能的工具,具备实时调整高速串行接口的多种参数、与系统其他模块通信及测量多通道误比特率等功能,支持所有的高速串行标准,包括:PCI Express、RapidIO、千兆以太网、XAUI等。使用IBERT核测试,只需通过JTAG接口下载设计并测试硬件,无需额外的管教和接口;大幅缩减了高速串行接口测试场景的建立和调试时间,是高速串行接口开发中理想的调试工具。

再次感谢您的热心回答。GTX我目前还在学习。

小编可以加个qq好友吗,我最近的任务是用FPGA实现SATA 协议,物理层也有用到gtx(rocket io),能不能交流一下

加好友可以,但是我是菜鸟,感觉很难帮的到你。qq:643184081