Vivodo 在Artix7中Setup time violation

时间:10-02

整理:3721RD

点击:

同一个工程,在K7的xc7k410tffg900-2上时序都ok。但我换成A7的xc7a15tftg256-2,时序就不能满足而且差很多。主要是在Data Path上,K7布局布线后只需要1.8ns,而K7确需要3.9ns。

求助我应该怎么解决哦?不修改逻辑的话能解决吗?

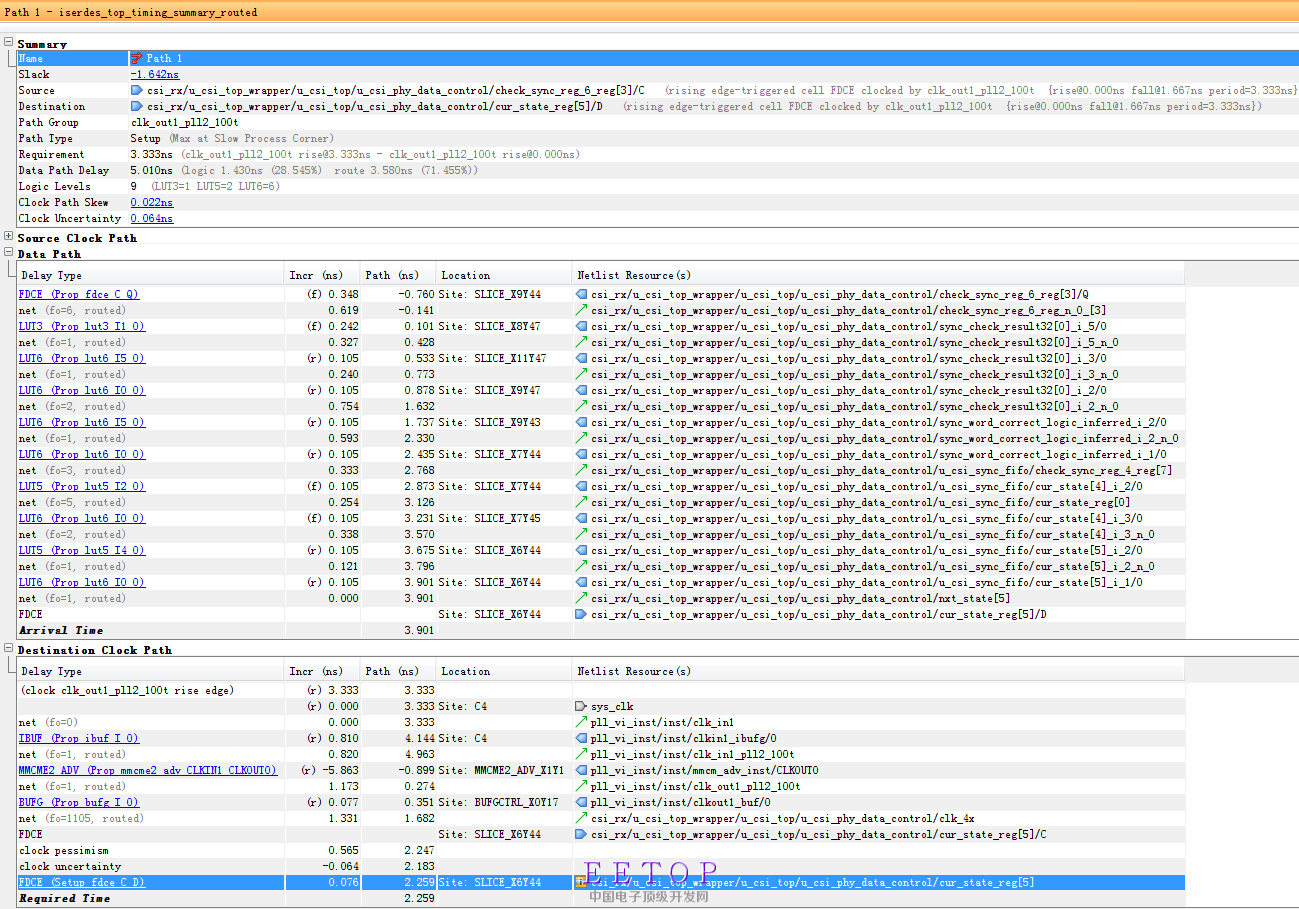

下图是两个设备布局布线后最差路径的时序报告:7a15t:

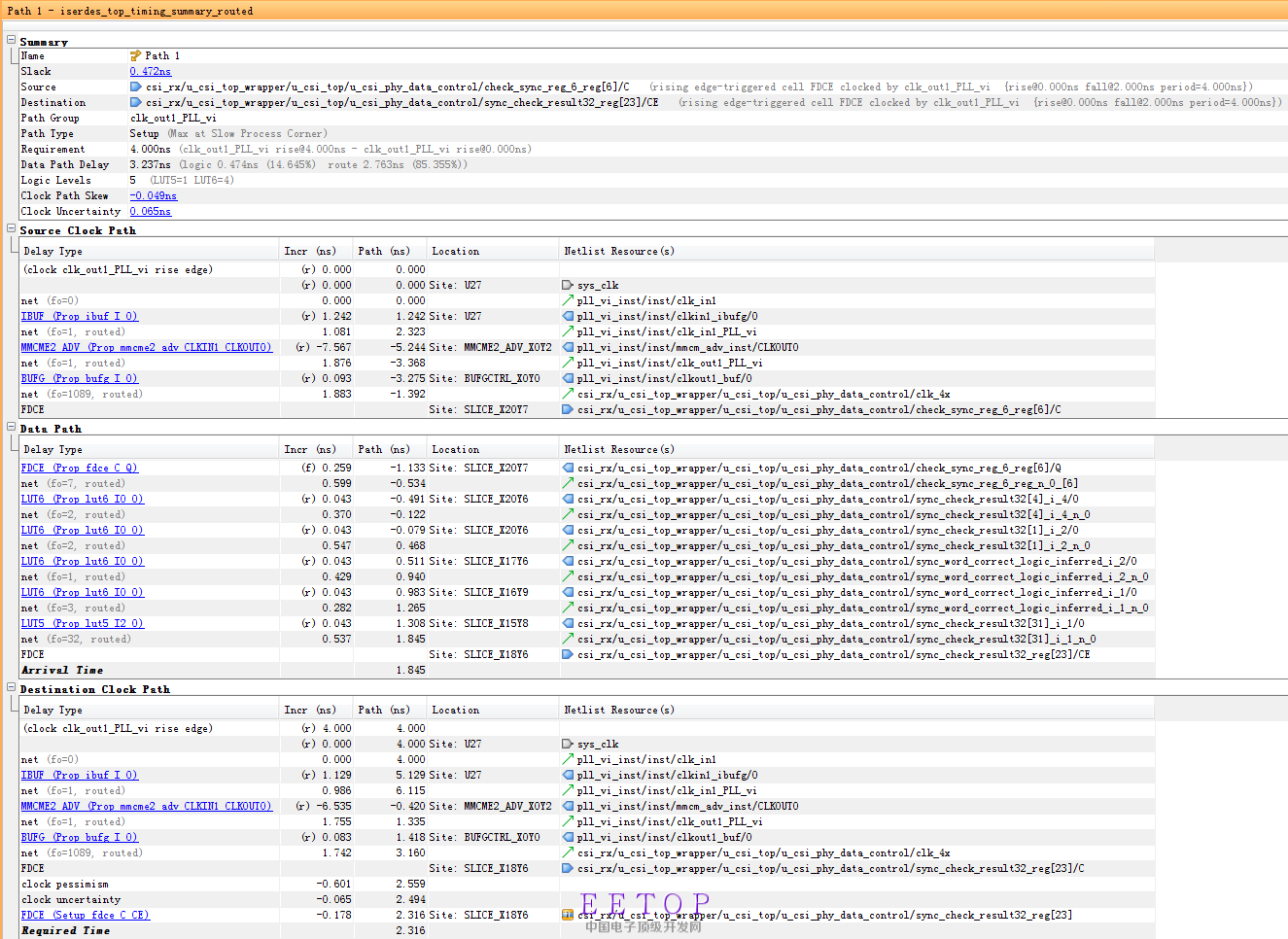

7k410t:

自顶。

小编,两个芯片的容量和performance差太远了。对于A7,如果整个系统的时钟(performance)要求在200M以下,资源利用率在70%以下,可以试一下,问题不大。

现在看你现在route占整个data path的70%多,感觉是资源利用率太高了,建议换个大点的芯片,比如a7 200t试一下。

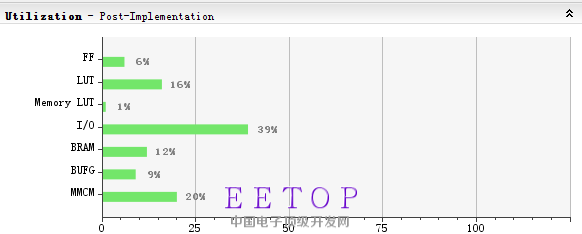

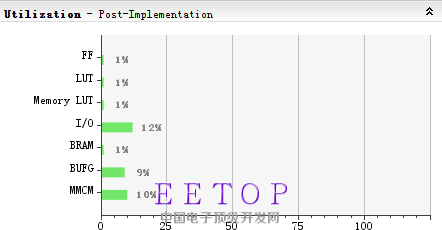

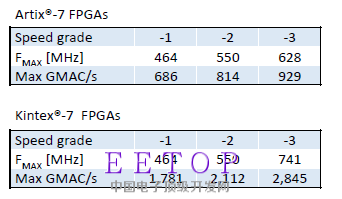

谢谢回答。可是我看报告资源利用都不高啊,我的project最关键部分都用的组合逻辑,但很奇怪K7的Data Path时间就很短。另外我速度等级都选的2,A7和K7不是一样的吗?

还有我也试过a7200t,route time比15t稍微好点,但也是和k7差很多。我实在是不明白了,为何速度等级一样,资源大小也差不多的,布局布线时候就差好多。求助

有个文档叫dc and swithch 你拿出来对比一下,应该就知道这两个器件的差异。

太感谢了,我再细看看那文档

首先确定你的时钟是走的全局时钟,其次试试多次优化

嗯。我的始终引脚都走的全局始终,然后过了一个mmcm,通过bufg出来使用。查了下a7和k7的DC and AC Switching Characteristics,delay差的不小啊,都快一半了。看来我要选a7的话只能修改下组合逻辑,尽量都用时序了吧