关于数据更新时刻的问题

各位论坛的大神, 小弟请教一个问题:在Verilog中,假设时钟为clk,复位信号为rst,某一控制信号为ctrl,现有寄存器A和B,当如下进程发生时:

always@(posedge clk or negedge rst)

begin

if(!rst)

B <= 0;

else if(ctrl)

B <= A;

end

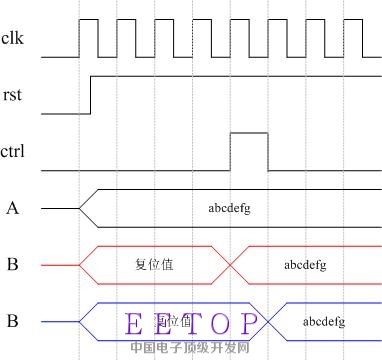

若clk、rst、ctrl和A的时序如下图所示:

那么B的更新发生是发生在上图图中的那个时刻呢?也就是说是红色的正确还是蓝色的正确?

还请群里的人解惑一下,谢谢啦!

可靠一点应该是蓝色

现在我有点儿凌乱,原因是当我控制信号ctrl采用testbench方式通过延时产生这样的一个波形时,然后用ModelSim仿真出来就是图中红色部分的结果;但是如果我再建一个module用来专门产生控制信号ctrl时,然后再新建一个顶层top将其连接起来,最后新建一个testbench只用来产生时钟,那么仿真出来的结果又是图中蓝色部分。请问哪一种可靠一些?

如果说clk和ctrl理论上在同一时刻上升沿重合,那么红色的就是正确的。但在现实世界中,clk和ctrl如果来自不同源,那么她们上升沿来到的相对时刻是不稳定的,不能得出红色还是蓝色准确的结论,但是在蓝色的起始时间,B肯定是已经变化了的,如果想要获得稳定的b,从蓝色时刻开始是没有问题的。如果这两个信号来自同一个源,就要看他们的走线长度,看谁先到达触发器,如果时钟先到达,就是蓝色正确。

我现在用两种手段仿真了一下:一是采用ctrl直接在testbench中产生,直接用“#延时”的方式控制ctrl的翻转,然后ModelSim仿真得到的结果是红色曲线;二是采用再新建一个module来生成ctrl,然后再新建一个顶层top将这两个模块整合例化,然后再对顶层top新建一个testbench,testbench中只描述clk和rst的行为,再进行ModelSim仿真,得到的结果却又是红色曲线部分。所以,我凌乱了。

貌似我在工程中,红蓝两种情况都遇到过。

私以为2点:

(1)clk能不能第一时间检测到ctr,关键是要看ctr与clk的相位关系到底是否满足建立保持时间。

如楼上所说,与是否同源,信号的延时的不同都有关系。

(2)实际编程情况中,要根据程序在芯片跑了之后的结果来看,功能仿真因为没考虑延时等情况,

所以仅供参考。

(3)在编写过程中,最好避免这种在同一时刻变化的情况,保证clk与被判断信号的相位有个180

度的偏差就自然不存在这个问题了。

非常感谢您的意见! 对于第(1)点我能理解;

但是第(2)点,我做的是AISC设计,在设计没有完成且没有流片前,没有芯片啊,所以您说的要考虑延时的情况是否可以在该工艺库进行后仿来进行?

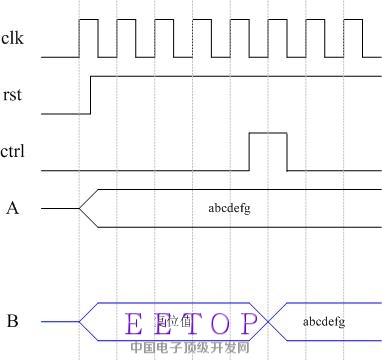

至于第(3)点,您的意思是控制信号ctrl最好是做成如下所示的情况吗?

也即控制信号不要在clk的上升沿时变化。

ASIC不是很了解,后仿其实我也不怎么用。后仿能不能排查这个问题,你试一下看看。

我用FPGA设计的时候一般直接用chipscope就可以看到程序实际运行的情况了。

第3点,你画的图就是我说的意思,但并不是所有信号都可以这样随意调整相位的,有时候可以这样做。

好的,明白了,ASIC的后仿就是带器件实际延时的仿真,应该跟你做FPGA用Chipscope Pro抓取实际仿真波形是一样的(我是做前端的,这个后端别人做,别人没做完后端我也不明后仿啊),只能从前端这个源头去避免吧。然后我懂您的意思了,谢谢!

考虑延时的,是前仿就需要考虑的,你设计的电路实际是什么样的,你要有个概念,不可能等到后仿才去考虑这些路径延时。因为实际电路在传输的时候是肯定有延时的,你不能从代码去推到电路结构,而应该是从电路结构来反推你的代码到底合理不合理,还是那句话,HDL是描述电路的语言,不是创造电路的语言。

(⊙o⊙)哦,受教了。那么请问在我设计的时候,为了避免延时的不确定性造成的干扰,我ctrl的值最好是在clk的上升沿期间保持稳定是吧?即如7楼(#7)图中所示的,是吗?

蓝色!讨论前提是ctrl是来自clk域下的信号,如果是异步信号,没啥好讨论的。

另外,所有DFF描述加一个delay,可以在RTL仿真时模拟实际电路的门延时,自己看着也方便。

always@(posedge clk or negedge rst)

begin

if(!rst)

B <= 0;

else if(ctrl)

B <= #DLY A;

end

如果你都按上面来描述,ctrl的沿也不会跟clk重合混淆自己了

楼上说的方法可以,但有些时候可能不能做到在上升沿保持稳定,因为有可能是同步时钟一直采样下来的。

如果ctrl信号是同步信号,那正确的应该是蓝色。出现红色的情况有一种可能是因为你在testbench中对ctrl信号的产生用的赋值是非阻塞赋值"=",如果用阻塞赋值"<="就不会有类似的额问题

楼上正解,其实只是一个简单的仿真问题。

如果testbench和dut使用同一个时钟clk,在testbench中这样写:@(posedge clk) ctrl=1'b1;,那么由于阻塞赋值立即使ctrl生效,在dut中就可以直接采样到ctrl变化后的值,就会出现红色的波形;

如果写成@(posedge clk) ctrl<=1'b1; 那么由于非阻塞赋值不能立即使ctrl生效,在dut中采样到的是ctrl变化前的值;

或者写成:@(posedge clk) #0 ctrl=1'b1; 在dut中采样到的是ctrl变化后的值。

4#正解