求助:Testbench中的initial和always问题?

时间:10-02

整理:3721RD

点击:

各位大神, 小弟最近在Testbench中使用initial和always分别给某一源代码测试激励时,发现在相同的激励下,使用initial和always语句得到的仿真结果不同。目前还没有找到原因所在,在此想问问大家,请大家帮帮忙,谢谢啦!

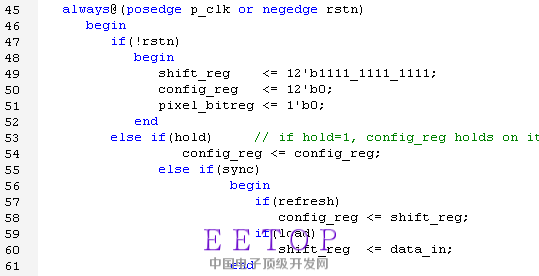

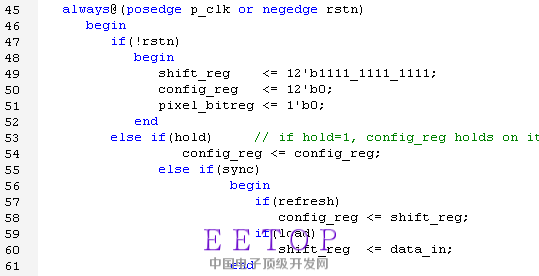

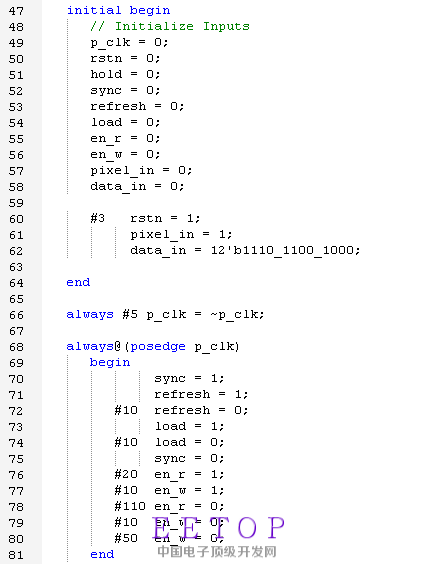

源代码中设计出问题的那部分代码如下:

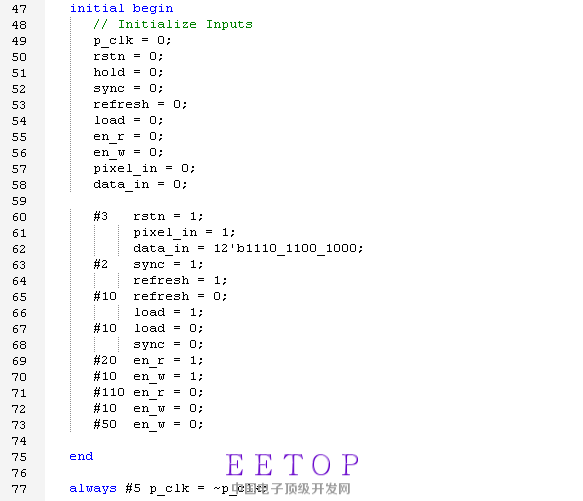

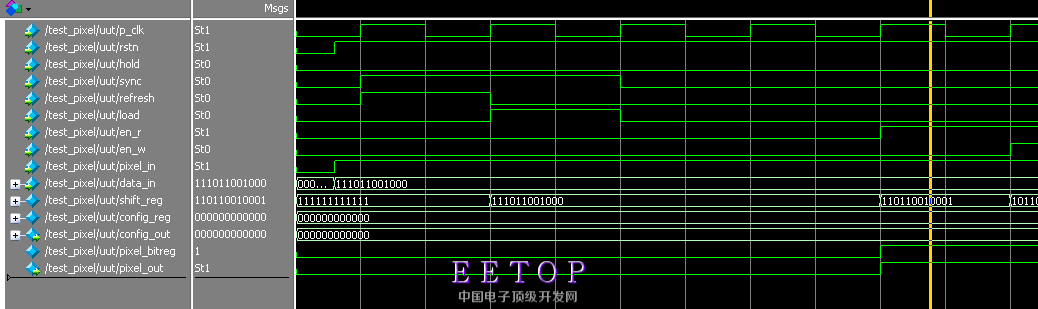

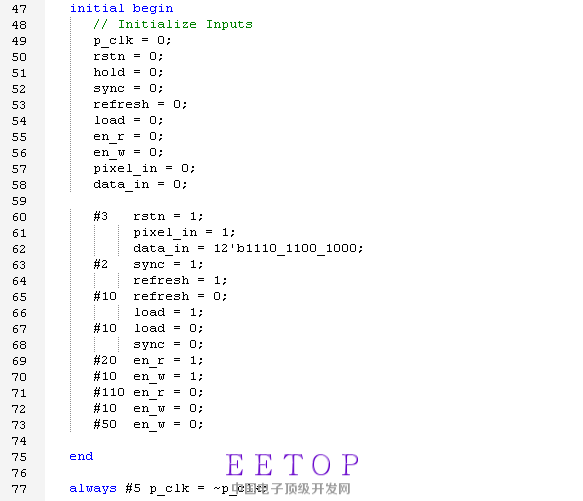

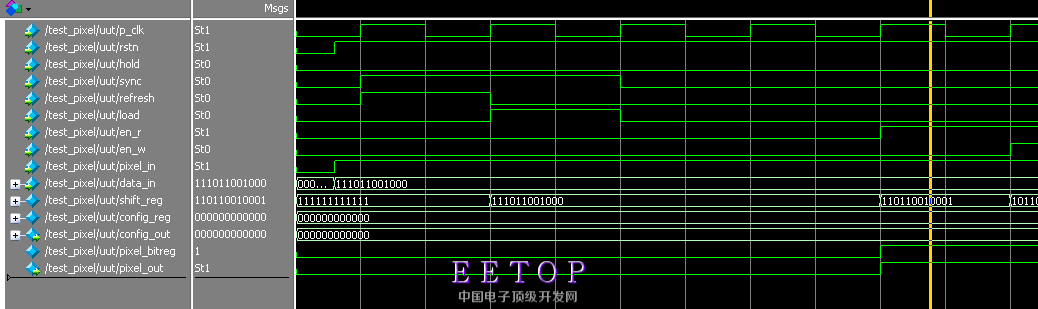

1) 当用initial给测试激励时,测试激励和仿真结果如下:

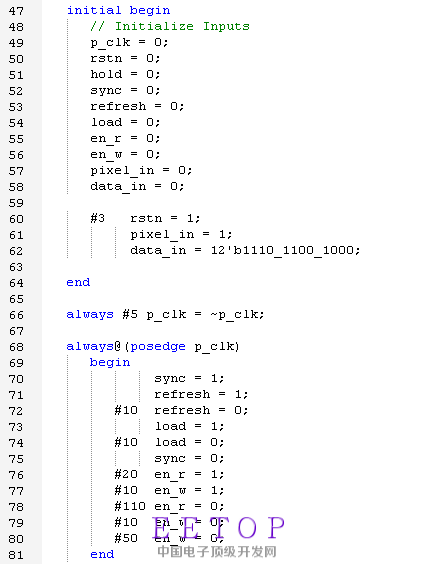

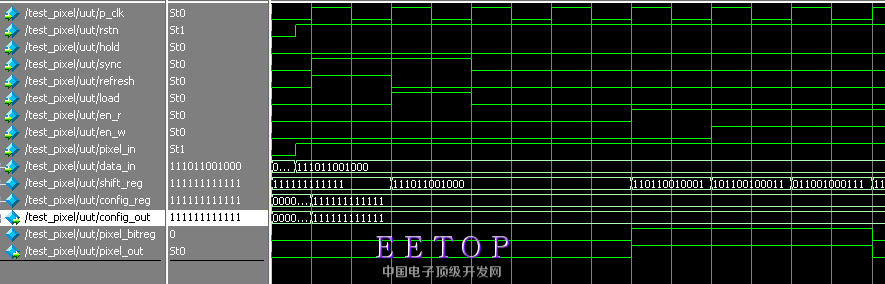

2) 当用always给测试激励时,测试激励和仿真结果如下:

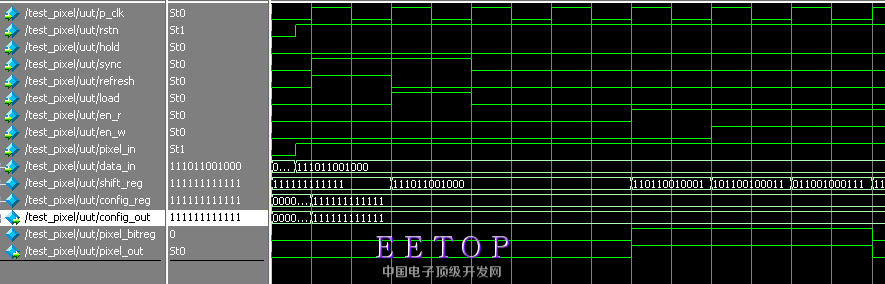

结合源代码,从仿真中可以明显的看出,在第一个时钟p_clk的上升沿到来,且信号sync和refresh为高电平时,寄存器config_reg变化不同(测试激励用initial写的仿真结果中,config_reg改变了;在测试激励用always写的仿真结果中,config_reg的值并没有更新)。

我想要的是第一种结果,也即initial给的测试激励形式,但是我又想让这些激励循环出现,所以就采用always来代替,但是代替之后,发现仿真结果却不同,这是为什么呢?请问有人知道吗?

源代码中设计出问题的那部分代码如下:

1) 当用initial给测试激励时,测试激励和仿真结果如下:

2) 当用always给测试激励时,测试激励和仿真结果如下:

结合源代码,从仿真中可以明显的看出,在第一个时钟p_clk的上升沿到来,且信号sync和refresh为高电平时,寄存器config_reg变化不同(测试激励用initial写的仿真结果中,config_reg改变了;在测试激励用always写的仿真结果中,config_reg的值并没有更新)。

我想要的是第一种结果,也即initial给的测试激励形式,但是我又想让这些激励循环出现,所以就采用always来代替,但是代替之后,发现仿真结果却不同,这是为什么呢?请问有人知道吗?

悄悄地顶一下!d=====( ̄▽ ̄*)b

只能说不建议这么用always。因为你每一次都是时钟上升沿触发,里面又有超过时钟周期的延时,可能会有时序上的冒险存在,很难去理解你这个进程的行为了,还不如用for循环去处理或者repeat()来实现你要的意思。

恩恩,好的,明白了,我以前在testbench里面也很少使用always,用的多的是repeat,for也用过……非常感谢您的答复,谢谢啦!

不客气,testbench可以用的更抽象点,不一定要满足可综合的语法。

好的,谢谢啦!