求助如何从近似周期性矩形波中求出特定一段的宽度?

时间:10-02

整理:3721RD

点击:

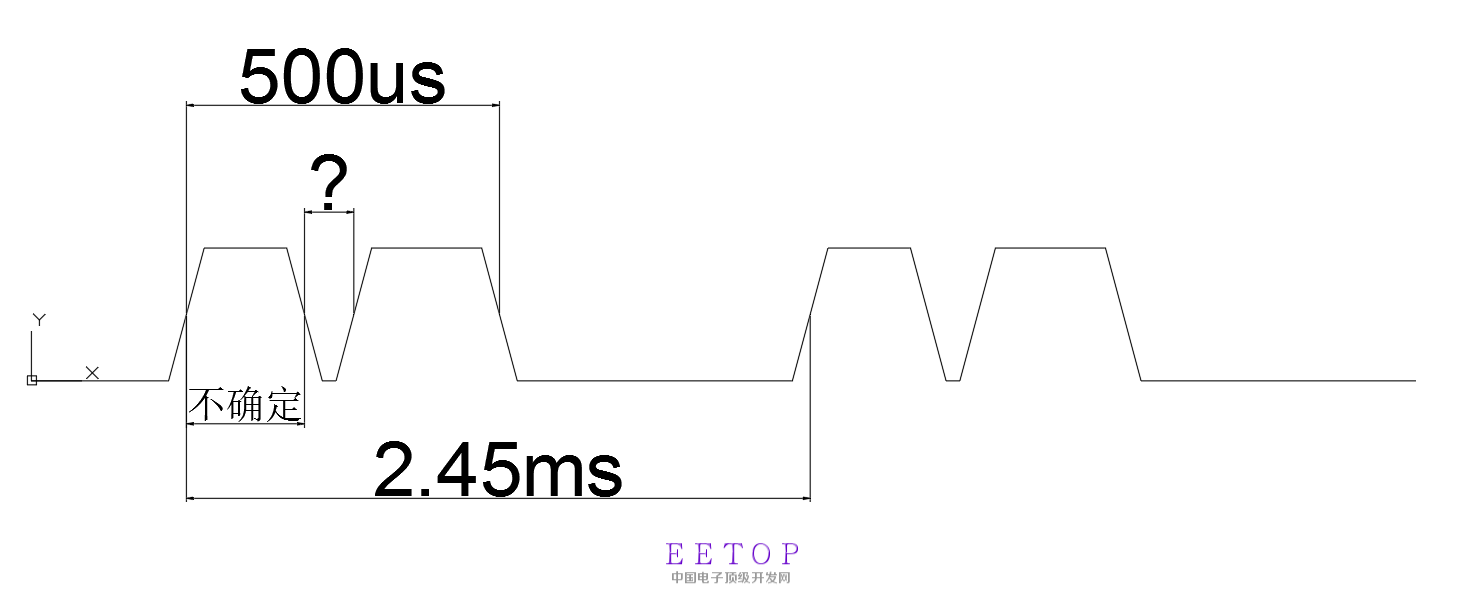

如上图,有一个近似周期性信号,一个周期2.45ms左右,各个矩形波波峰或波谷的宽度可能略有变化,但变化不超过5us,我想知道用verilog如何能求出“?”那一段的宽度。因为本人非电子专业,基本知识严重不足,所以也请求大神们推荐点处理这种问题的书籍或者相关的基础知识的书籍,不胜感激!

real stamp_f, stmp_r, stmp_f_dly;

always @(posedge clk)

begin

stamp_r = $realtime;

stmp_f_dly = stmp_f;

@(negedge clk);

stmp_f = $realtime;

end

real diff = stmp_r - stmp_f_dly;

基本思想就是这样,你自己再做一个奇偶变化的信号,这样保留前一个diff值,舍去后一个diff值。

就是最基本的verilog语法。找一本大学教材就够了。

非常感谢!虽然现在还没看懂,我学点语法再来研究。

另外还想请教一下,上面这段代码是不是可综合的呢?好像看到有说real是不可综合的。若想要综合,又该怎么编写呢?