FPGA时序约束失败,求助!

时间:10-02

整理:3721RD

点击:

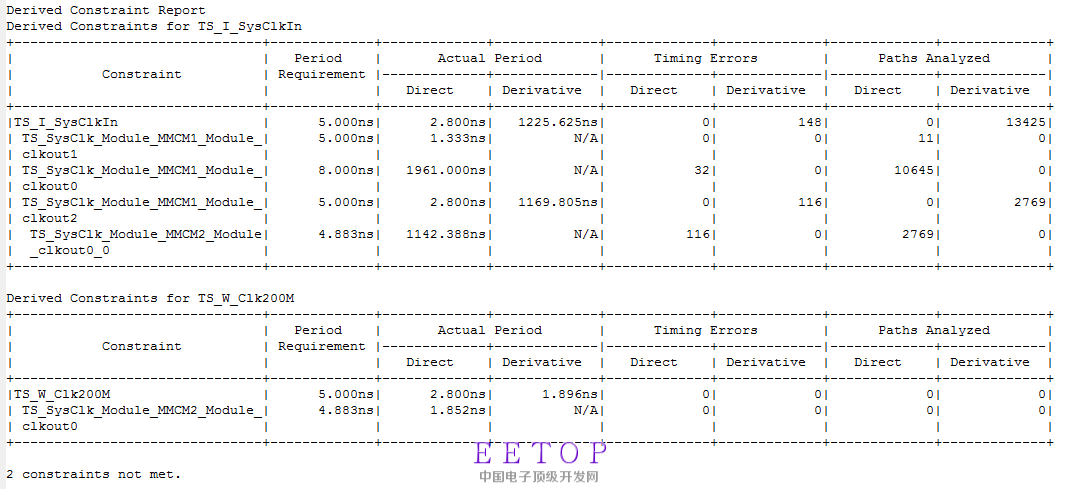

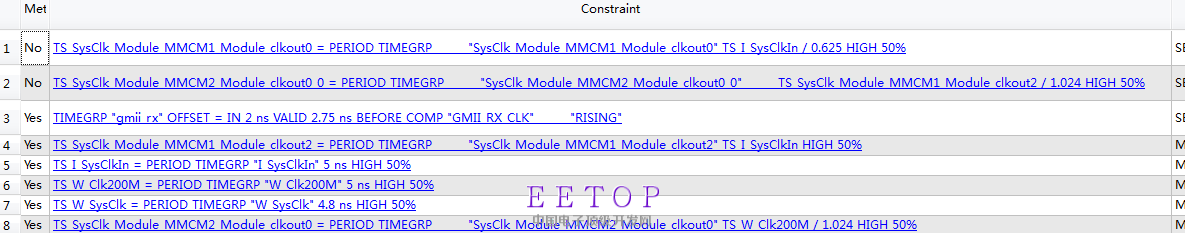

时序约束失败,timing score都140958了,芯片是xilinx virtex-6, 200M差分晶振时钟输入(I_SysClkIn_p,I_SysClkIn_n),调用了2个MMCM串联,约束失败的路径就是这2个MMCM导致的,我在UCF中约束了周期,不知道这个约束具体怎么产生的,求大神解惑,不胜感激。代码如下:

- MMCM1_Module MMCM1_Module

- (// Clock in ports

- .CLK_IN1_P ( I_SysClkIn_p ), // IN

- .CLK_IN1_N ( I_SysClkIn_n ), // IN

- // Clock out ports

- .CLK_OUT1 ( O_EthClk ), // OUT 125M

- .CLK_OUT2 ( O_EthRefClk ), // OUT 200M

- .CLK_OUT3 ( W_Clk200M ), // OUT

- // Status and control signals

- .LOCKED ( )); // OUT

- MMCM2_Module MMCM2_Module

- (// Clock in ports

- .CLK_IN1 ( W_Clk200M ), // IN

- // Clock out ports

- .CLK_OUT1 ( W_SysClk204p8M ), // OUT

- // Status and control signals

- .RESET ( 1'b0 ), // IN

- .LOCKED ( )); // OUT

时序报告如下图: