xilinx 7series vc707 DDR3读写控制问题

时间:10-02

整理:3721RD

点击:

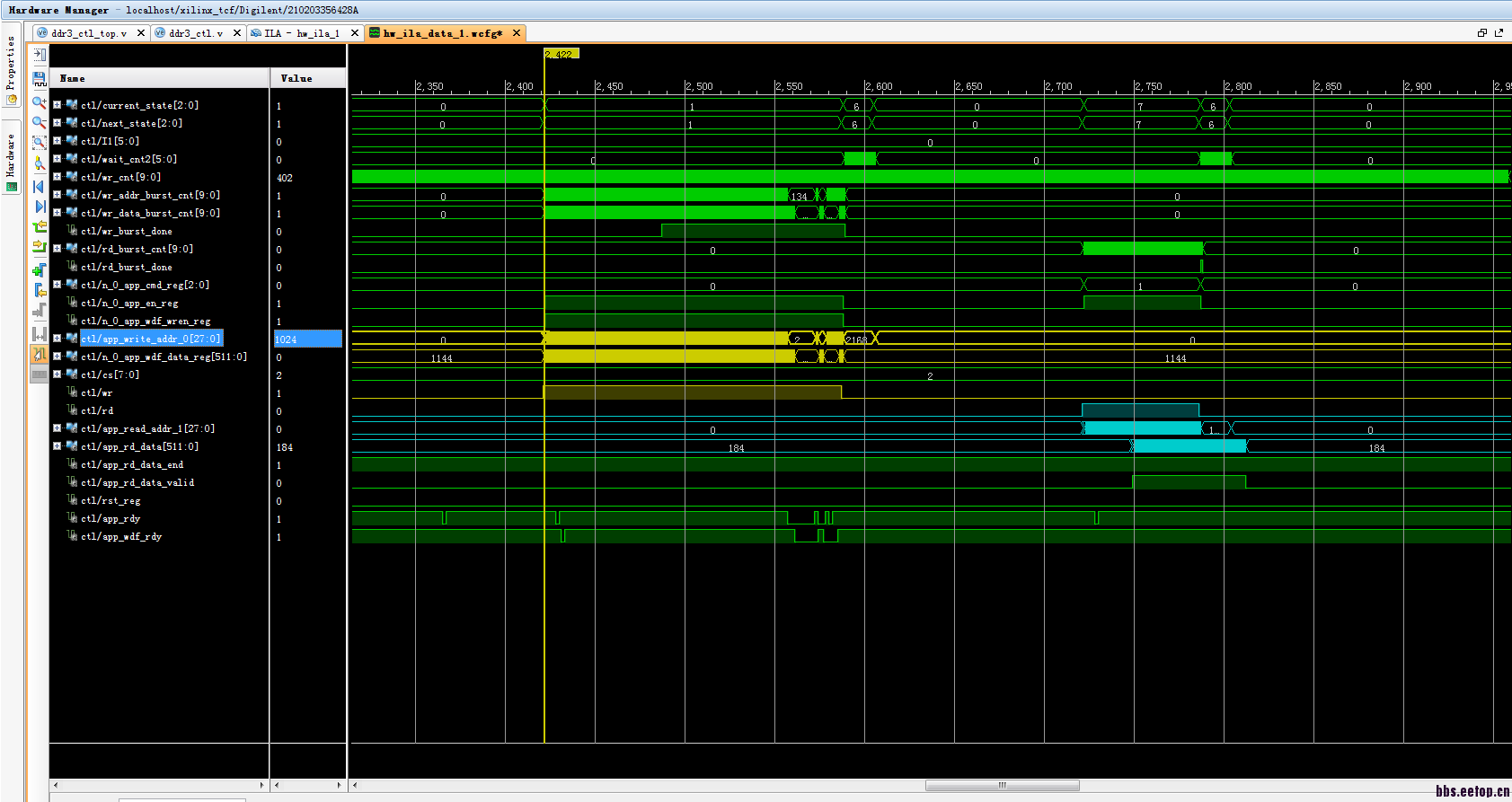

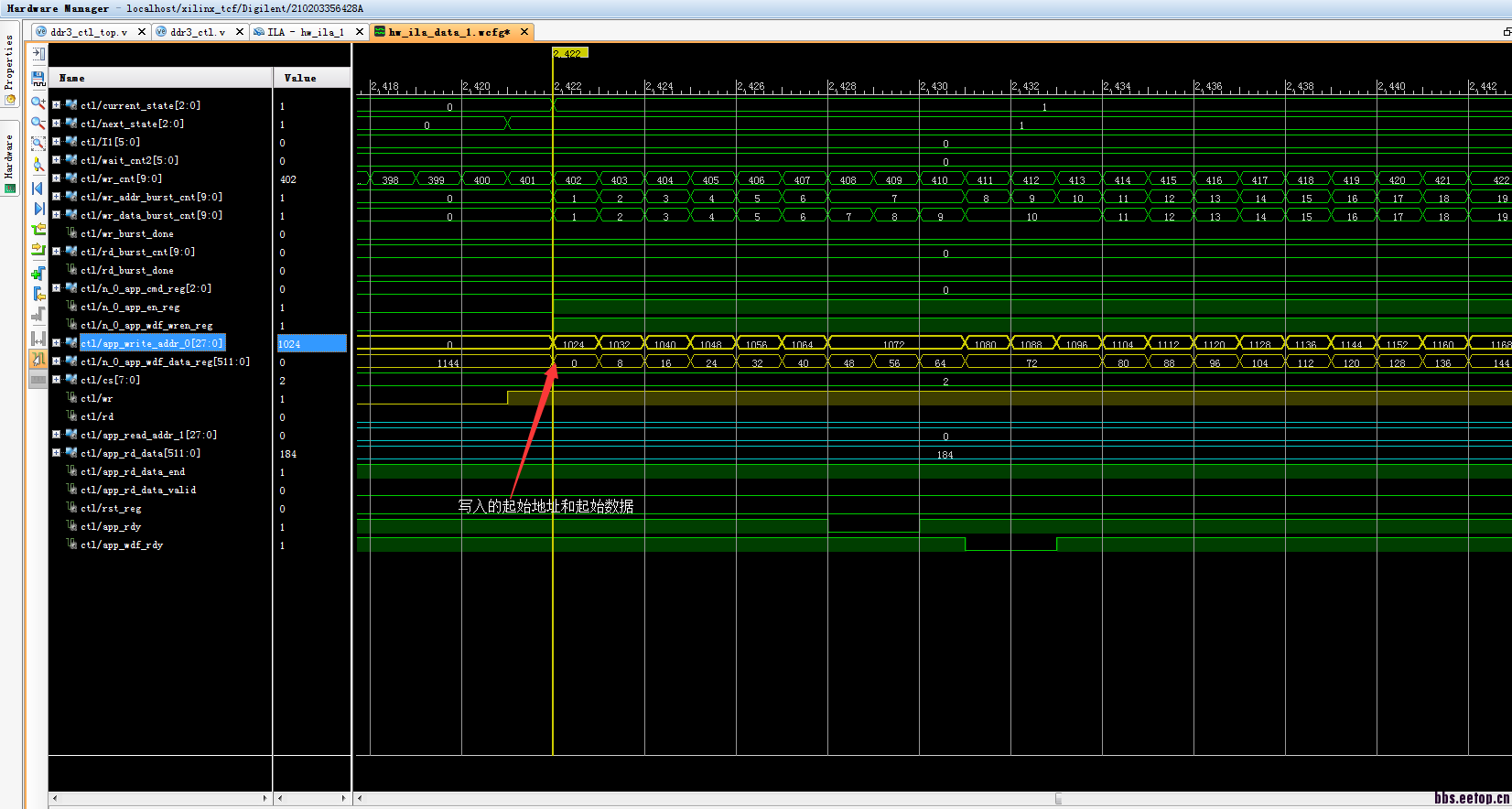

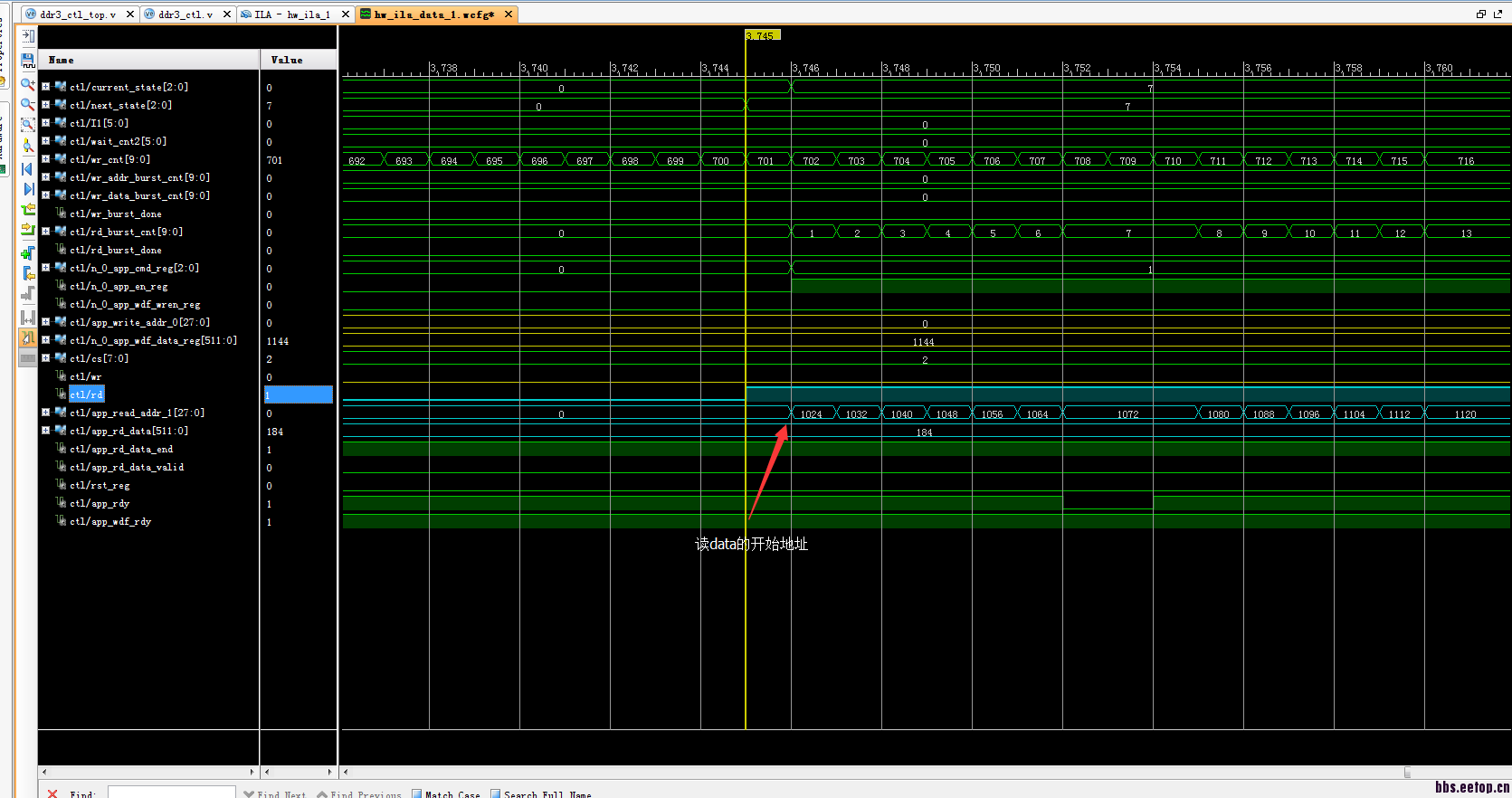

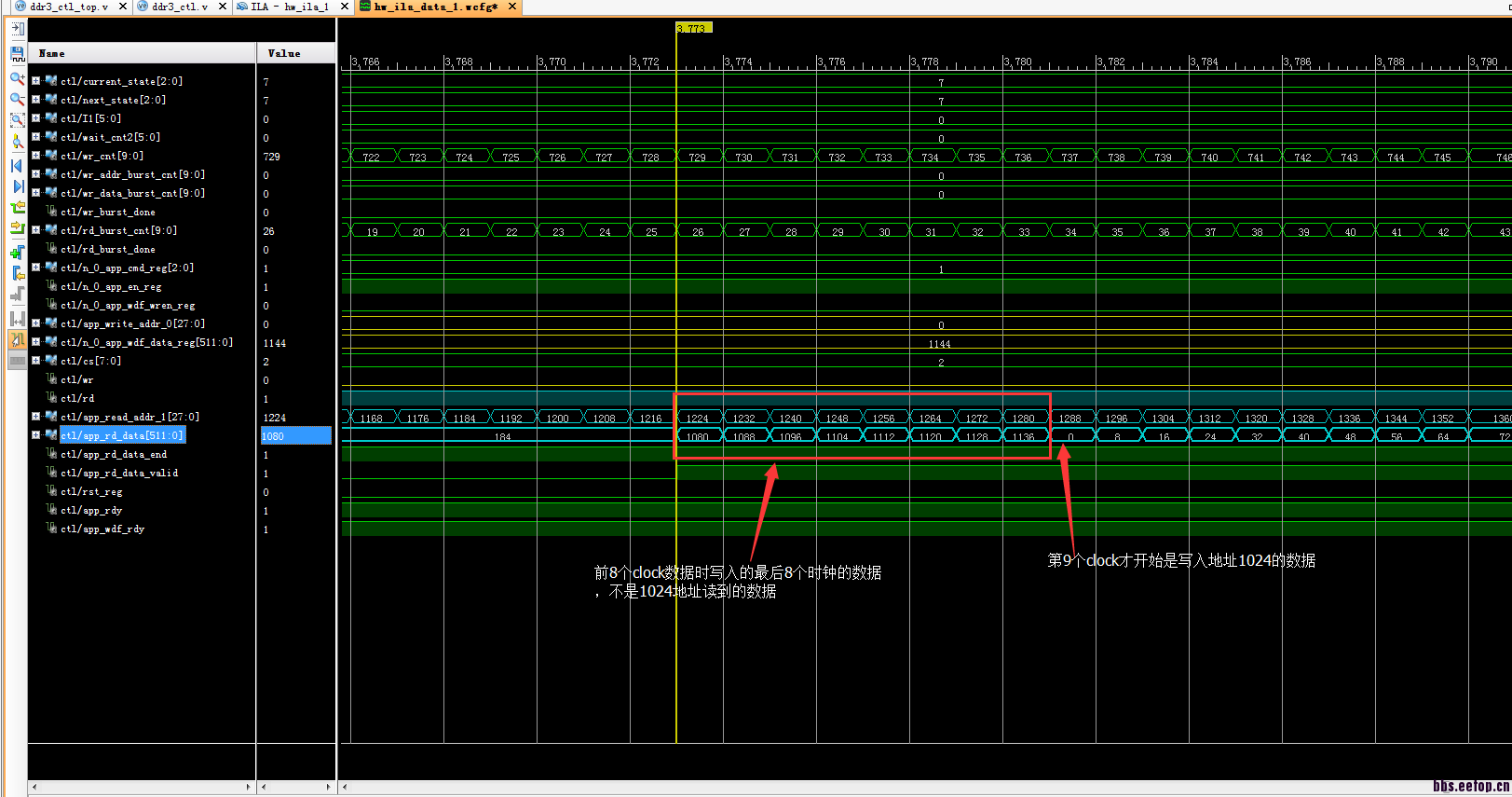

测试代码的结构是根据计时器发送读请求,进入写状态,以write_addr=1024为首地址写入若干个时钟data,然后经过若干时钟发送一个读请求,读出1024-XXXX地址的数据,波形图如下所示:黄色波形为写请求、写地址、写数据;蓝色波形为读请求、读地址、读数据。

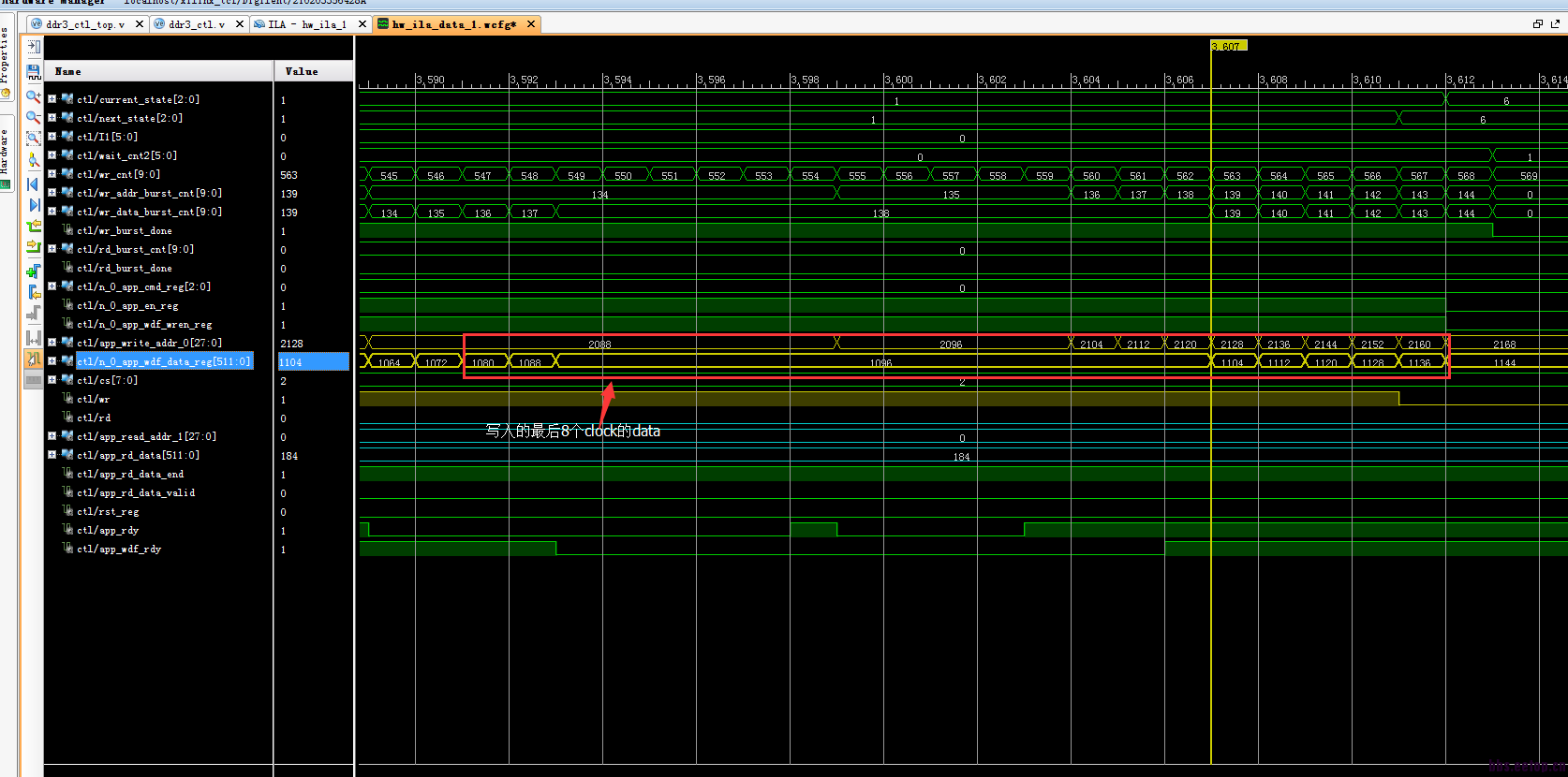

那么问题来了,每次读出来的前8个clock的数据,都是写数据时写进去的最后8个clock的数据,第9个clock才是写入地址1024的data。代码修改很多次,没有检查出导致这个问题的逻辑错误,刚接触这个板子,对这个板子的ddr3的内部连接不很清楚,不知道是不是内部fifo导致这个问题,求大神帮助,感激不尽!每次改代码都要跑半个小时,累觉不爱了!

我调试的ddr3感觉能写进去,但是读不出来,app_rd_data_valid一直为低,app_en,app_cmd,app_addr是按手册上给的,但是app_rd_data_valid一直为低,能否指导一下?或者把你的测试代码让我参考参考,不胜感激!邮箱:xd240@163.com

应该 是地址那里吧

你的DDR3应该是SODIMM DDR3 存储器 1600Mbps吧,与芯片可能有所 不同的

,应该是你自己弄错了,看了一下你的图形,RD是读的操作,数据有效要到下一个时钟周期才是有效的。RD不是数据的VALID。

围观一下学习学习

好好看文档

问题之前就解决了,再来回复下。

出现错误的原因是:写地址fifo与写数据fifo不同步导致的,在第一个写周期,写入地址fifo的地址数比写入数据fifo的数据的数目少8个,因此在数据fifo中残留个8个数据,到了第二个写周期被写入到开始的8个clk。

文档中没有看到这种触发式读写的时序图,所以开始根据文档的时序出现了这个错误~感谢楼上各位回复。

不好意思,我问题解决后就没上这个网站了。你的问题解决了么?

小编,请问尝试将DDR3封装成一个FIFO 或BRAM 了吗? 加Q:445097329,相互交流学习下!

没有做后续的工作了

How to configure ddr3 any manual?