serdesip核以及lvds的仿真

时间:10-02

整理:3721RD

点击:

仿真不正确,明明clk_div_out1有数值.dataout竟然没有数值.是什么原因呢,还有各种时钟,lvds的,都没有数值显示,这是为什么。

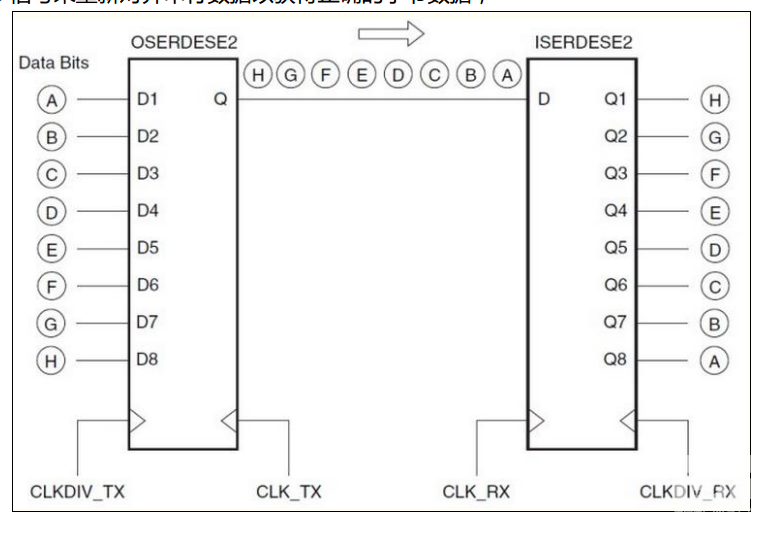

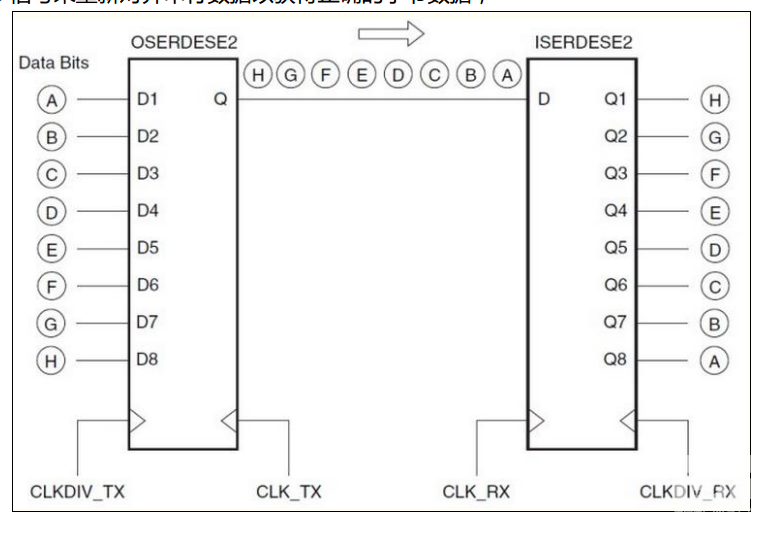

原理图如下:

与所编写的程序有所出入。主要是时钟的部分。

真正的rtl图示:只截取并转串的一部分截图。

主程序如下:

`timescale 1ns / 1ps

module Serdes_Test(

input clk_50m,//全局时钟

input rstn, //复位

input clk_reset,

input clk_in_from_pin_p, //lvds时钟输出P

input clk_in_from_pin_n, //lvds时钟输入N

input data_in_from_pin_p, //lvds输入数据P

input data_in_from_pin_n, //lvds输入数据N

output clk_out_to_pin_p, //lvds时钟输出P

output clk_out_to_pin_n, //lvds时钟输出N

output data_out_to_pin_p, //lvds输出数据P

output data_out_to_pin_n //lvds输出数据N

);

wire clk_div_out_1; //低速时钟1,串行发送时钟的8分频

wire clk_div_out_2; //低速时钟2,串行接收时钟的8分频

wire [7:0] datain; //LVDS输入的8位并行数据

//产生LVDS发送的测试数据,0~FF

reg [7:0] dataout;

always @(posedge clk_div_out_1) begin

//always @(posedge clk_50m) begin

if (~rstn)

dataout <= 0;

else if (dataout == 8'hff)

dataout <= 0;

else

dataout <= dataout + 1'b1;

end

//产生BITSLIP信号,用于修改串转并的Bit的起始位置

wire [7:0] data_delay;

reg BITSLIP=1'b0;

reg slip_check;

reg equal=1'b0;

assign data_delay=datain;

always @(posedge clk_div_out_2)

begin

if (~rstn)

slip_check <= 1'b0;

else if(data_delay==8'h80) //当串转并的输入的数据为0x80的时候,检测开始

slip_check <= 1'b1;

else

slip_check <= 1'b0;

end

always @(posedge clk_div_out_2)

begin

if (~rstn) begin

BITSLIP <= 1'b0;

equal<=1'b0;

end

else if((slip_check==1'b1) && (equal==1'b0))

if (data_delay ==8'h81) begin //如果检测到数据0x80后面的下一个时钟的数据为0x81时

BITSLIP <= 1'b0; //BITSLIP不为高

equal<=1'b1; //数据正确信号为高

end

else begin

BITSLIP <= 1'b1; //BITSLIP产生一个高脉冲,改变串转并的数据排列

equal<=1'b0; //数据正确信号为低

end

else begin

BITSLIP <= 1'b0;

equal<=equal;

end

end

//并转串,8位数据dataout转换成串行数据,并通过lvds差分信号输出

wire dataout_w;

assign dataout_w=dataout;

p_to_s p_to_s_inst

(

// From the device out to the system

.data_out_from_device(dataout_w), //Input pins

.data_out_to_pins_p(data_out_to_pin_p), //Output pins

.data_out_to_pins_n(data_out_to_pin_n), //Output pins

.clk_to_pins_p(clk_out_to_pin_p), //Output pins

.clk_to_pins_n(clk_out_to_pin_n), //Output pins

.clk_in(clk_50m), // Single ended clock from IOB

.clk_div_out(clk_div_out_1), // Slow clock output

// .clk_reset(clk_reset),

// .io_reset(~rstn) //system reset

.clk_reset(1'b0),

.io_reset(1'b0) //system reset

);

//串转并,LVDS差分信号转换成单端信号再通过串转并,转换为8位数据datain

s_to_p s_to_p_inst

(

// From the system into the device

.data_in_from_pins_p(data_in_from_pin_p), //Input pins

.data_in_from_pins_n(data_in_from_pin_n), //Input pins

.data_in_to_device(datain), //Output pins

.bitslip(BITSLIP), //Input pin

.clk_in_p(clk_in_from_pin_p), // Differential clock from IOB

.clk_in_n(clk_in_from_pin_n), // Differential clock from IOB

.clk_div_out(clk_div_out_2), // Slow clock output

// .clk_reset(clk_reset),

// .io_reset(~rstn) //system reset

.clk_reset(1'b0),

.io_reset(1'b0) //system reset

);

endmodule

激励文件如下:

module sim(

input clk_50m,//全局时钟

input rstn, //复位

input clk_reset,

input clk_in_from_pin_p, //lvds时钟输出P

input clk_in_from_pin_n, //lvds时钟输入N

input data_in_from_pin_p, //lvds输入数据P

input data_in_from_pin_n, //lvds输入数据N

output clk_out_to_pin_p, //lvds时钟输出P

output clk_out_to_pin_n, //lvds时钟输出N

output data_out_to_pin_p, //lvds输出数据P

output data_out_to_pin_n //lvds输出数据N

);

Serdes_Test U1(

.clk_50m(clk_50m),

.rstn(rstn)

);

reg rst_n_reg;

reg clk_50m_reg;

assign rstn=rst_n_reg;

assign clk_50m=clk_50m_reg;

initial

begin

rst_n_reg=1'b0; #80 rst_n_reg=1'b1;

clk_50m_reg=1'b1; forever #4 clk_50m_reg=~clk_50m_reg;

end

endmodule

仿真文件如下:

原理图如下:

与所编写的程序有所出入。主要是时钟的部分。

真正的rtl图示:只截取并转串的一部分截图。

主程序如下:

`timescale 1ns / 1ps

module Serdes_Test(

input clk_50m,//全局时钟

input rstn, //复位

input clk_reset,

input clk_in_from_pin_p, //lvds时钟输出P

input clk_in_from_pin_n, //lvds时钟输入N

input data_in_from_pin_p, //lvds输入数据P

input data_in_from_pin_n, //lvds输入数据N

output clk_out_to_pin_p, //lvds时钟输出P

output clk_out_to_pin_n, //lvds时钟输出N

output data_out_to_pin_p, //lvds输出数据P

output data_out_to_pin_n //lvds输出数据N

);

wire clk_div_out_1; //低速时钟1,串行发送时钟的8分频

wire clk_div_out_2; //低速时钟2,串行接收时钟的8分频

wire [7:0] datain; //LVDS输入的8位并行数据

//产生LVDS发送的测试数据,0~FF

reg [7:0] dataout;

always @(posedge clk_div_out_1) begin

//always @(posedge clk_50m) begin

if (~rstn)

dataout <= 0;

else if (dataout == 8'hff)

dataout <= 0;

else

dataout <= dataout + 1'b1;

end

//产生BITSLIP信号,用于修改串转并的Bit的起始位置

wire [7:0] data_delay;

reg BITSLIP=1'b0;

reg slip_check;

reg equal=1'b0;

assign data_delay=datain;

always @(posedge clk_div_out_2)

begin

if (~rstn)

slip_check <= 1'b0;

else if(data_delay==8'h80) //当串转并的输入的数据为0x80的时候,检测开始

slip_check <= 1'b1;

else

slip_check <= 1'b0;

end

always @(posedge clk_div_out_2)

begin

if (~rstn) begin

BITSLIP <= 1'b0;

equal<=1'b0;

end

else if((slip_check==1'b1) && (equal==1'b0))

if (data_delay ==8'h81) begin //如果检测到数据0x80后面的下一个时钟的数据为0x81时

BITSLIP <= 1'b0; //BITSLIP不为高

equal<=1'b1; //数据正确信号为高

end

else begin

BITSLIP <= 1'b1; //BITSLIP产生一个高脉冲,改变串转并的数据排列

equal<=1'b0; //数据正确信号为低

end

else begin

BITSLIP <= 1'b0;

equal<=equal;

end

end

//并转串,8位数据dataout转换成串行数据,并通过lvds差分信号输出

wire dataout_w;

assign dataout_w=dataout;

p_to_s p_to_s_inst

(

// From the device out to the system

.data_out_from_device(dataout_w), //Input pins

.data_out_to_pins_p(data_out_to_pin_p), //Output pins

.data_out_to_pins_n(data_out_to_pin_n), //Output pins

.clk_to_pins_p(clk_out_to_pin_p), //Output pins

.clk_to_pins_n(clk_out_to_pin_n), //Output pins

.clk_in(clk_50m), // Single ended clock from IOB

.clk_div_out(clk_div_out_1), // Slow clock output

// .clk_reset(clk_reset),

// .io_reset(~rstn) //system reset

.clk_reset(1'b0),

.io_reset(1'b0) //system reset

);

//串转并,LVDS差分信号转换成单端信号再通过串转并,转换为8位数据datain

s_to_p s_to_p_inst

(

// From the system into the device

.data_in_from_pins_p(data_in_from_pin_p), //Input pins

.data_in_from_pins_n(data_in_from_pin_n), //Input pins

.data_in_to_device(datain), //Output pins

.bitslip(BITSLIP), //Input pin

.clk_in_p(clk_in_from_pin_p), // Differential clock from IOB

.clk_in_n(clk_in_from_pin_n), // Differential clock from IOB

.clk_div_out(clk_div_out_2), // Slow clock output

// .clk_reset(clk_reset),

// .io_reset(~rstn) //system reset

.clk_reset(1'b0),

.io_reset(1'b0) //system reset

);

endmodule

激励文件如下:

module sim(

input clk_50m,//全局时钟

input rstn, //复位

input clk_reset,

input clk_in_from_pin_p, //lvds时钟输出P

input clk_in_from_pin_n, //lvds时钟输入N

input data_in_from_pin_p, //lvds输入数据P

input data_in_from_pin_n, //lvds输入数据N

output clk_out_to_pin_p, //lvds时钟输出P

output clk_out_to_pin_n, //lvds时钟输出N

output data_out_to_pin_p, //lvds输出数据P

output data_out_to_pin_n //lvds输出数据N

);

Serdes_Test U1(

.clk_50m(clk_50m),

.rstn(rstn)

);

reg rst_n_reg;

reg clk_50m_reg;

assign rstn=rst_n_reg;

assign clk_50m=clk_50m_reg;

initial

begin

rst_n_reg=1'b0; #80 rst_n_reg=1'b1;

clk_50m_reg=1'b1; forever #4 clk_50m_reg=~clk_50m_reg;

end

endmodule

仿真文件如下: