请教有熟悉ALTLVDS_RX 的吗!

我对高速ADC进行采集,ADC的输出数据是一个差分时钟,八个差分数据

首先,我用的片子是CYCLONE IV E 没有专门的LVDS模块,所以看过一些书,上面说的方法都用不上,

有的说用外部PLL,把PLL配置成LVDS模式等等,但实际是PLL无法配置成LVDS模式(或许是片子不支持吧,反正配置不了),

而且书上说LVDS配置为外部PLL模式时,就会出现某些端口可以跟PLL连接,实际是,配置成外部PLL模式,这些接口也不可用!

而且这个系列也不支持动态配置功能!

另外,用内部的PLL模式时,我有两个疑问:

1,时钟输入源选什么?我原来想当然的是将ADC的随路时钟差分转单后给LVDS的rx_inclock,不过这样的话无法编译

我用外部晶振的时钟输入,这样可以编译,但没有用到随路时钟的话,怎么保证接收到的数据是正确的,LVDS模块本身也不可能知道数据的中心在哪里!

2,在配置LVDS时有个rx_data_align可选,好像是说可以对数据进行一定的延时,但这个信号是怎么用的,手册上好像也没写(我总觉得ALTERA的手册跟屎似的,远没有XILINX的好用),每次延时多少时间也不知道!

3,LVDS串转并后的时序是怎么对应的手册上也没有,ALTERA都不知道画个时序图吗!

唉,有哪位高手熟悉吗,

如果没有猜错的话你用的adc是LVDS电平标准的,只需管脚配置为相应电平标准(当然FPGA的硬件配置要支持,BANK电压为2.5V)出来的时钟实际上就是数据同步时钟,用于直接采样即可。管脚直接配置为LVDS标准即可,这种ADC很常见,一般有两种模式,一种是SDR模式,一种是DDR模式。

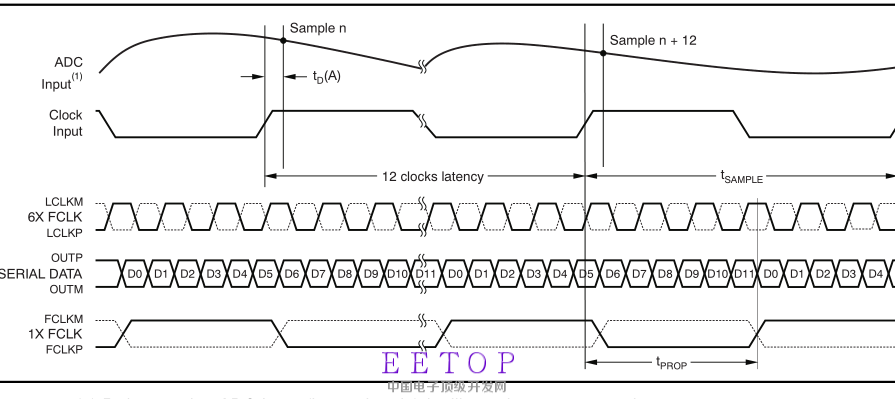

ADC的输出信号如下图:

有随路时钟不错,不过数据速率为480MHz,还是比较高了吧,

如果直接用随路时钟进行采集的话,由于时钟与数据到达寄存器的时间不同,采集的数据可能会出问题吧

确实速度很高,我以为你的ADC是并行的数据输出。随路时钟是480MHz?还是数据速率是480Mbps?

因为如果是480Mbps,你的Cyclone E还可以拼一下,如果是480MHz,也就是说你的数据速率是960Mbps,那就不用玩了,你的这个片子不支持那么高的速率,Cyclone GX带收发器的也就875Mbps;

数据速率是480MHz,随路时钟240MHz

另外你用过LVDS吗?不是专用模块哪种(CYCLONE IV没有专用模块,都是搭建),

是采集时钟的上升沿和下降沿同时采集吗?先不考虑时序的问题的话我功能仿真出来都有问题

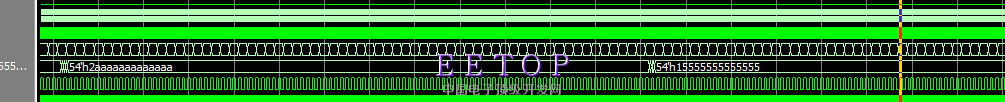

我9个通道给的都是固定的0101010101。,串解因子为8的时候,所以考虑采集起点的问题,LVDS出来不该是固定的555555或aaaaaaa吗

但我仿真出来的图如下:周期性的一会是1555555555..一会是2aaaaaaaaaa..且从155555555到2aaaaaaa的中间有一些数据不稳定,什么原因呢?

在提醒里能看到你说的一部分,我用过LVDS_RX(经常用),在Cyclone IV E这样的片子上是没有收发器硬核的,所以你在定制IP核的时候很多都是不可用的(DPA是灰色的,所以没有动态相位对齐的功能),仅仅使用了LVDS接口标准传输数据,其实这样的IP和在实现的时候和你写的普通DDR电路是一样的,要靠时序约束来做,在Cyclone IV E上我实现过250MHz SDR的采样速率,而且还是并行13位的ADC输出。你这是串行的,电路做的不是太差,并且时序约束做好,还是可以实现的。加油。

非常感谢,我再看看,等我的电路板到了,调试时再看看会有什么情况!

看到了,在LVDS RX中牵扯到一个比特滑动的问题,需要滑动比特或者同步,定制IP的话里面有一个Bitslip选项,你勾上,你的ADC的FCLKM就是用作同步的。你可以研究一下。

你说的应该是rx_data_align这个信号吧,我就是不是很清楚这个信号是怎么用的呢!能给我讲一下吗,所谓的比特滑动具体指什么意思呢,关于rx_data_align,我在ALTERA的资料里没找到详细的讲解啊!

我的理解是:

默认情况下 一个并行输出是D0到D7,D8到D15.....

如果给rx_data_align一个脉冲的话,一个并行输出就成了D1到D8,D9到D16.....

如果再给rx_data_align一个脉冲的话,一个并行输出就成了D2到D9,D10到D17.....

是这个意思吗?

能不能再咨询一个关于LVDS的问题?我原来的思路是:

1,通过PLL产生一快一慢两个时钟

2,对 随路时钟和帧时钟作为数据一起采集

3,通过对随路时钟进行采集、判断调节PLL相移

4,通过对帧时钟进行采集、判断调节比特滑移

配置管脚时发现,随路时钟和帧时钟是专用时钟脚,不支持IO REG,所以这种方式不行了,

就算我改变一下方式,可以使用随路时钟进行采集,但无法对帧时钟进行采集,不还是无法对齐吗?

你有没有什么好的方法呢!专用时钟引脚有使用上还有别的什么限制吗?谢谢

不会吧,你要采集随路时钟?大可不必啊(也不太可能),首先你就不要用LVDS_RX这个IP核了,不适用在你这个设计里,可能会很麻烦。自己做一个DDR采样电路,根据你的ADC时序特性对你的电路进行时序约束。以FCLKM作为输入同步脉冲就可以了(FCLKM上升沿是D0比特是确定的)。

直接用随路时钟进行采集吗?这样的话,随路时钟到名寄存器的延时与数据到寄存器的延时就可能有差别,通过约束限制吗?另外FCLK怎么对齐呢,这个脚是用的专用引脚,好像不能直接到register ,这样的话还是不能作同步啊?

还有一个时钟引脚配置成LVDS后,在文件里只使用正时钟的上升沿、下降沿采集就可以了是吧,不管负时钟!在XILINX里好像有本地时钟,这样的话可以最小话延时,ALTERA有吗?

你现在ADC这个时钟其实就是采样时钟,要是用于随路时钟,大可不必和数据同步翻转,只需要同源即可,这个随路时钟就是采样用的,不是给你用作PLL输入的。差分管脚只是在pin planner做一下约束就可以了,和你代码没关系,你代码就做DDR电路实现就可以了。剩下的时序问题就交给时序约束了。看你的ADC时序特性,同步电路约束很简单。

如果随路时钟为DCLK(240MHz),数据为DATA(480Mbps)

先用DCLK的双沿采集,再用上升沿对齐,产生DATA2(240Mbps)

同时对DCLK分频生成DCLK2(120MHz),再用DCLK2的双沿采集,然后上升沿对齐,产生DATA3(120Mbps)

最后对DCLK2分频生成DCLK3(60MHz),再用DCLK3的双沿采集,然后上升沿对齐,产生DATA4(60Mbps)

添加约束,这样是否可行

第一次做这么高速的,很多地方都不清楚,还望高手不吝赐教!

你这么做是怎么想的?上升沿采数据放在寄存器1,下降沿采数据放在寄存器2,最后形成两个一半的数据,再用同一个时钟采样到完整的数据寄存器不就可以了?或者时序上想省事也可以直接用FIFO将两个沿隔离起来,最后再读端同步。

我是想尽量将频率降低一点,如果用同一个时钟合在一起的话,时钟频率还有120MHz,

小编你好,我想问一个LVDS_RX的问题。

我使用cycloneV做一个AD采集系统,当ALTLVDS_RX配置成使用外部PLL时,对应rx_clock,rx_in,和rx_enable连接到PLL输出时fitter通不过,出现与限制冲突错误。想问问你这几个信号应该分别怎么连接呢?谢谢了

你这是源同步采样