问个仿真奇怪的问题

时间:10-02

整理:3721RD

点击:

有两种写法://---------------------

// RTL-A

//---------------------

wire #10ns in_d = in;

wire a;

assign a= (in===in_d) ? in:in_d;

//---------------------

// RTL-B

//---------------------

wire #10ns in_d = in;

reg b;

always @(*)

begin

b = (in===in_d) ? in:in_d;

end

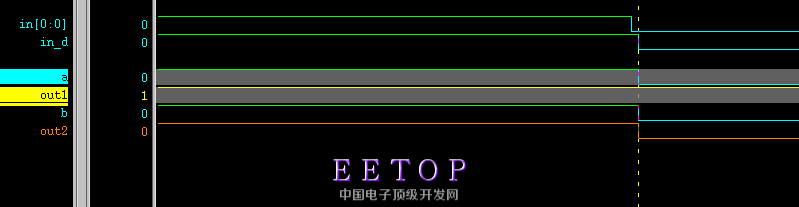

VCS仿真时候,a和b信号波形是完全一致的。

但是使用a和b的时候,out1和out2却不一样。

reg out1;

always @(*)

begin

if(a) begin

#1000;

out1 = 1;

end

else begin

out1 = 0;

end

end

reg out2;

always @(*)

begin

if(b) begin

#1000;

out2 = 1;

end

else begin

out2 = 0;

end

end

当a和b同时产生下降沿的时候,out1(由a驱动)不变0,但是out2(由b驱动)立刻变0.

为什么会这样?