分频时钟出现不定态的问题?

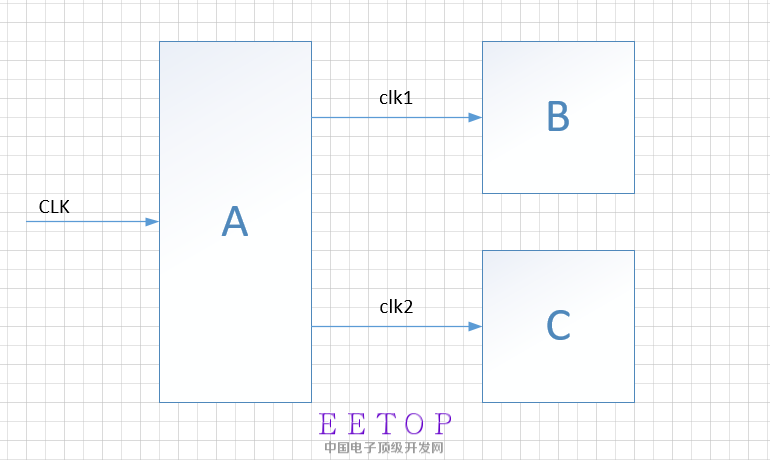

就是说我的一个时钟分频模块A,将CLK分频后得到分频时钟clk1和clk2,将clk1给模块B,将clk2给模块C,如下图2所示:

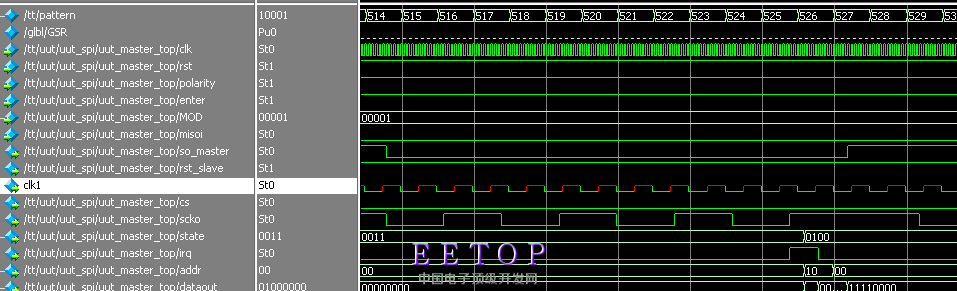

仿真时,clk1的结果如上图1所示,其在由低电平跳到高电平的时候出现了不定态X,但是如果将A与B的连线去掉,得到clk1分频时钟就不存在这个问题,出来的分频时钟clk1正常。

我的clk1逻辑是如下面这样描述的:

always@(posedge CLK or negedge rst)

begin

if(!rst)

begin

count <= 3'b0;

clk1 <= 1'b0;

end

else if(count == 3'b011)

begin

clk1 <= ~clk1;

count <= 3'b0;

end

else

count <= count + 1'b1;

end

请问有人知道出现这个问题的原因吗?

問題應該是在module B

我猜module B 的clk_in 應該有宣告錯誤或是 tie low 的情形

明显是模块B有问题,可能clk_in定义错了

非常抱歉,请问“宣告错误”是什么呀?“tie low”又是什么?这两个不懂,还请大神再解释一下,谢谢!

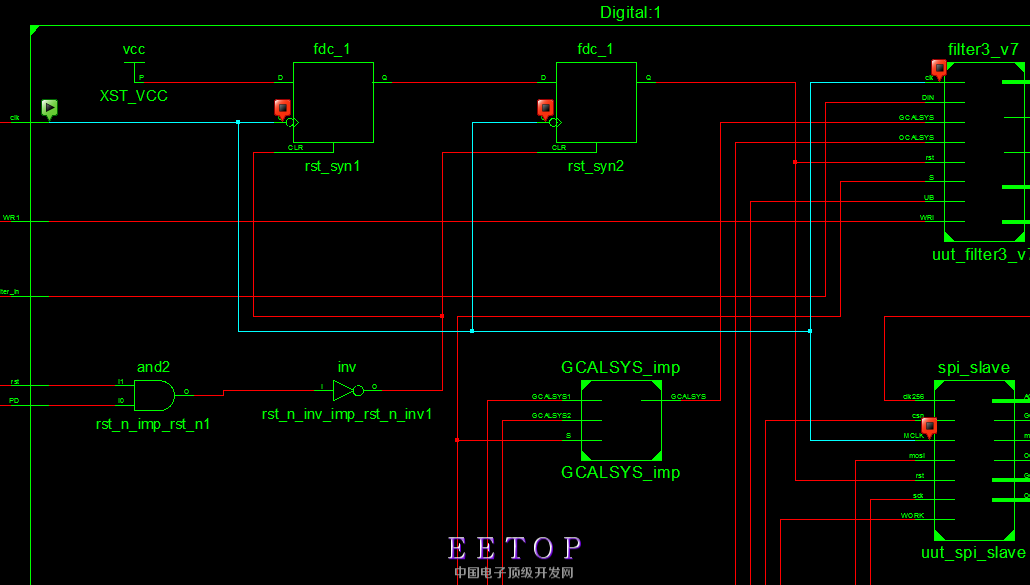

我检查了一下,然后进行分区域排除,发现问题确实出现在模块B,但是我检查了一下模块B的clk_in,发现没有定义错误啊,定义的是input类型。(模块B由模块d和e组成,送给模块B的时钟实质上是送给了d和e),还是没有检查出问题所在。我实际的设计如下图所示:

上述将的模块B就相当于这里的整个Digital模块,模块d和e就相当于这里的filter3_v7和spi_slave模块,前面两个D触发器是用作异步复位同步释放逻辑的。

非常感谢各位的帮助,问题已经找到了。原因是将A,B,C三个模块例化得到顶层的一个模块时(假设命名为U0),其主时钟定义为clk,然后内部模块B的时钟名称也是定义为clk,在编写整个顶层(针对U0)的Testbench时,输入reg clk应该是指U0的主时钟,但是后面又通过语句assign uut.uut_B.clk = 0将模块B的clk给引出来了,导致两个clk发生冲突,所以才产生了这个问题。

非常感谢各位的帮助,问题已经找到了。其原因是在将A,B,C三个模块例化封装成一个顶层模块(假设命名为U0)时,U0的时钟的名称被定义为clk,而此前Digital的时钟也被定义为clk,在编写Testbench的过程中,其内部本应该主时钟为U0的主时钟clk(定义为reg clk),这个没有问题,但是在内部却又通过语句assign

uut.uut_B.clk = 0 将模块B的时钟clk给印出来了,而且还是wire型,并赋了初始值0,这样就造成了U0和B的时钟clk定义冲突,所以才出现了上述问题。

B这一级没问题,可能是下面的D/E的问题。

前面的宣告,指的是定义,台湾那边的讲法。

tie low,是指固定接0。

assign uut.uut_B.clk = 0

這個描述就是tie low

恩恩,学习了,非常感谢,问题已经解决了,是Testbench中出现了整个系统的主时钟clk,又出现了模块B的主时钟clk,由于这两个时钟同名,且类型不同,所以就造成了冲突,导致出现了上述问题,非常感谢您!

搜嘎,这样子啊,果然如你们所说的那样子,谢谢啦,非常感谢!