对“异步复位同步释放”设计的一些疑问

时间:10-02

整理:3721RD

点击:

论坛中的各位好,小弟在做“异步复位同步释放”设计时产生了两个问题,自己一时半会没办法解决或者得不到验证,特来论坛里请教一下大神。问题如下:

1. 假设某一个系统System,其内部包含模块A、B、C、D等,内部模块A、B、C、D的内部又有其他小模块,……,反正就是一层一层的嵌套,现 在复位信号准备用“异步复位同步释放”设计,那么请问:这个异步复位同步释放设计是只需要做在整个系统的顶层上就可以了呢?还是在所有的 内部模块中都需要做异步复位同步释放设计?

2. 异步复位同步释放主要的有点是大大降低或者避免复位信号出现亚稳态的问题,具体来说就是在复位信号(这里假设低电平有效)release时, 如果release操作出现在时 钟上升沿(这里假设时钟上升沿有效)时刻或者紧贴时钟上升沿,那么就会出现亚稳态问题。我想问的是异步复 位同步释放可以避免复位信号由 于外界因素干扰而出现的毛刺问题吗?比如复位信号在复位过程中出现了一个时间很短的正脉冲,那么做了 异步复位同步释放之后,这个高脉冲是否会造成复位的误动作?又或者在系统正常工作时,由于外界因素的干扰造成复位信号由无效状态(为高 电平)出现了一个持续时间很短的负脉冲,此时这个负脉冲是否会使系统发生误动作,即造成系统复位了?

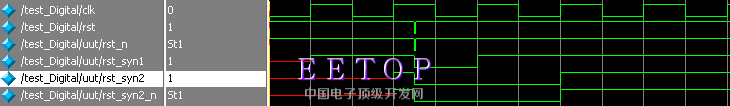

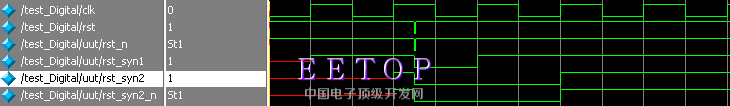

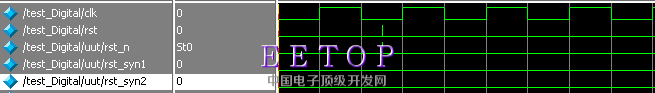

针对问题2的疑惑,我也做了一个验证,ModelSim仿真结果如下图所示:

从图中可以看到,正脉冲毛刺可以被异步复位同步释放设计给剔除掉,但是负脉冲毛刺却无法被剔除,这是怎么回事呢?

1. 假设某一个系统System,其内部包含模块A、B、C、D等,内部模块A、B、C、D的内部又有其他小模块,……,反正就是一层一层的嵌套,现 在复位信号准备用“异步复位同步释放”设计,那么请问:这个异步复位同步释放设计是只需要做在整个系统的顶层上就可以了呢?还是在所有的 内部模块中都需要做异步复位同步释放设计?

2. 异步复位同步释放主要的有点是大大降低或者避免复位信号出现亚稳态的问题,具体来说就是在复位信号(这里假设低电平有效)release时, 如果release操作出现在时 钟上升沿(这里假设时钟上升沿有效)时刻或者紧贴时钟上升沿,那么就会出现亚稳态问题。我想问的是异步复 位同步释放可以避免复位信号由 于外界因素干扰而出现的毛刺问题吗?比如复位信号在复位过程中出现了一个时间很短的正脉冲,那么做了 异步复位同步释放之后,这个高脉冲是否会造成复位的误动作?又或者在系统正常工作时,由于外界因素的干扰造成复位信号由无效状态(为高 电平)出现了一个持续时间很短的负脉冲,此时这个负脉冲是否会使系统发生误动作,即造成系统复位了?

针对问题2的疑惑,我也做了一个验证,ModelSim仿真结果如下图所示:

从图中可以看到,正脉冲毛刺可以被异步复位同步释放设计给剔除掉,但是负脉冲毛刺却无法被剔除,这是怎么回事呢?

出现正脉冲之后的仿真结果

顶一下,求助!

1)一般有一个专门做各个模块的不同时钟域的复位信号的同步电路的模块,换句话说,就是你说的各内部模块的复位信号的同步全部放在一个专门的模块中去做

2)异步复位中的毛刺无效态(高电平)会被过滤,有效态(低电平)因为是异步复位,自然是不会被虑掉的,你理解下“异步”这个词的含义。

1. 可能需根据你的功能决定, 如果内部模块没有特殊要求,可以在顶层做一个复位同步即可;如果内部模块对复位时序有要求,要详细考虑;

2. 正常给你的复位信号已经经过滤毛刺电路了, 复位信号不会有毛刺, 需要做的就是同步撤离; 而对于异步复位时候内部电路的毛刺, 电路要保证一个最低的复位宽度即可;

受教了,非常感谢!

谢谢,受教了,非常感谢!(原来正常给的复位信号已经经过去毛刺处理了)

跟樓上意見有些不一樣,有冒犯之處還請見諒

Ans 1: 哪裡做同步都沒有關係,重點是每個clock 都要做同步

Ans 2: Reset input pad 一般是schmitt trigger ,如果glitch level超過 schmitt trigger threshold voltage. 就會導致誤動作。

没事没事,各抒己见嘛,您这样说我觉得也有道理啊。