vivado仿真IP核遇到问题。

时间:10-02

整理:3721RD

点击:

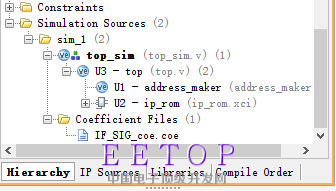

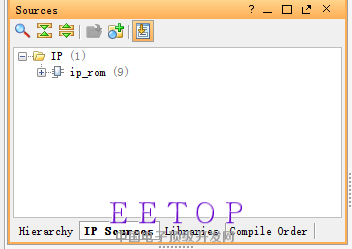

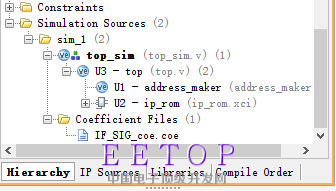

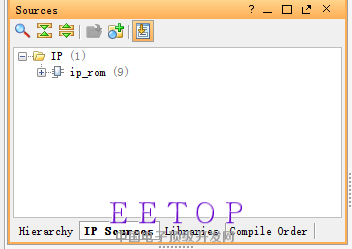

我以前用的ALTERA与quartus软件,现在用xinlinx和vivado软件。quartus用的还算明白,是用的altera-modelsim仿真。但是我在用vivado软件仿真时遇到了问题,我建立工程,写几行小代码,然后在单击ip catalog,创建了一个单口rom,并用.coe文件进行了初始化,我的代码很简单,就是读取rom中的内容,但是点击run simulation就是一个提示框一闪而过,都看不清是怎么回事,然后一切照旧,没有任何变化,我不知道错在哪里了。没有用到ip catalog时倒是能仿真,加了个ip rom就不行了,不知道哪里出问题了。另外ip integrator是干什么用的?会不会还得用到它。代码与贴图如下(代码个人认为不会出问题,先看图,代码可以不看):

module top_sim(

input reg clk,

input reg rst_n,

output[15:0] data_out

);

initial

begin

rst_n=1'b0;#40 rst_n=1'b1;

clk=1'b1; forever #5 clk=~clk;

end

top U3(

.clk(clk),

.rst_n(rst_n),

.data_out(data_out)

);

endmodule

module top(

input clk,

input rst_n,

output[15:0] data_out

);

wire[11:0] address;

address_maker U1(

.clk(clk),

.rst_n(rst_n),

.address(address)

);

ip_rom U2(

.clka(clk),

.ena(1'b1),

.addra(address),

.douta(data_out)

);

endmodule

module address_maker(

input clk,

input rst_n,

output[11:0] address

);

reg[11:0] address_reg;

always@(posedge clk or negedge rst_n)

if(!rst_n) address_reg<=12'd0;

else address_reg<=address_reg+1'b1;

assign address=address_reg;

endmodule

module top_sim(

input reg clk,

input reg rst_n,

output[15:0] data_out

);

initial

begin

rst_n=1'b0;#40 rst_n=1'b1;

clk=1'b1; forever #5 clk=~clk;

end

top U3(

.clk(clk),

.rst_n(rst_n),

.data_out(data_out)

);

endmodule

module top(

input clk,

input rst_n,

output[15:0] data_out

);

wire[11:0] address;

address_maker U1(

.clk(clk),

.rst_n(rst_n),

.address(address)

);

ip_rom U2(

.clka(clk),

.ena(1'b1),

.addra(address),

.douta(data_out)

);

endmodule

module address_maker(

input clk,

input rst_n,

output[11:0] address

);

reg[11:0] address_reg;

always@(posedge clk or negedge rst_n)

if(!rst_n) address_reg<=12'd0;

else address_reg<=address_reg+1'b1;

assign address=address_reg;

endmodule

补充:ip catalog与ip integrator到底是什么关系?

现在做好了,乱点乱按的东西太多了,重新开始做了一下可以了。没有问题,感谢大家的关注。

求教一下小编 具体怎么解决这个仿真一闪而过的问题的啊,,,我现在遇到了不知道怎么搞

我就是重新做了一遍就好了,也不知道为什么,应该多点了东西,所以仿真出了问题。