Testbench 波形 请教

时间:10-02

整理:3721RD

点击:

小弟初来乍到,还请大家多多指教。最近开始学Verilog,很多问题不懂。希望能够得到大家的帮助。

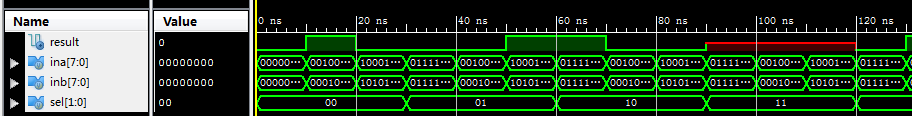

我想在testbench生产这样一个波形:

有个2位信号sel,产生前10ns为00,后面每30ns 加1的波形。如下

0 10ns 40ns 70ns 100ns 130ns.......

00 00 01 10 11

但我现在只能产生30ns循环的波形。code如下

- `timescale 1ns / 1ps

- module Test;

- // Inputs

- reg [7:0] ina;

- reg [7:0] inb;

- reg [1:0] sel;

- // Outputs

- wire result;

- // Instantiate the Unit Under Test (UUT)

- M_compare uut (

- .ina(ina),

- .inb(inb),

- .sel(sel),

- .result(result)

- );

- initial begin

- // Initialize Inputs

- ina = 0;

- inb = 0;

- sel = 0;

- end

-

- always

- begin

- #10 ina = 8'h23;

- #10 ina = 8'h8A;

- #10 ina = 8'h79;

- end

-

- always

- begin

- #10 inb = 8'h15;

- #10 inb = 8'hAC;

- #10 inb = 8'h79;

- end

- always #30 sel=sel+1;

-

- endmodule

把always用forever替换。

initial begin

sel = 0;

#10 sel = 1;

forever begin

#30;

sel = sel + 1;

end

end

楼上正解

十分感谢,顺利解决。

新手学些了!