JESD204B 帧组合问题

时间:10-02

整理:3721RD

点击:

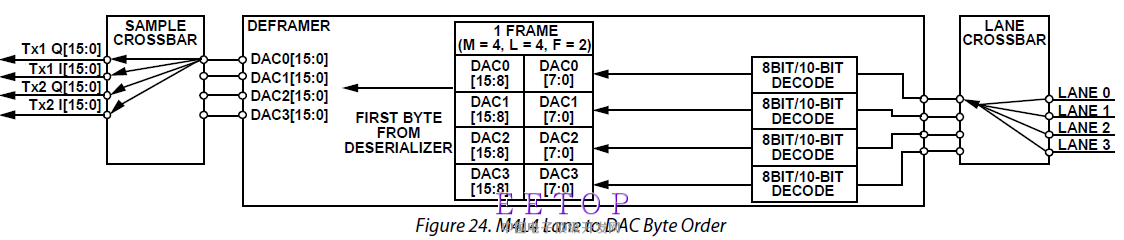

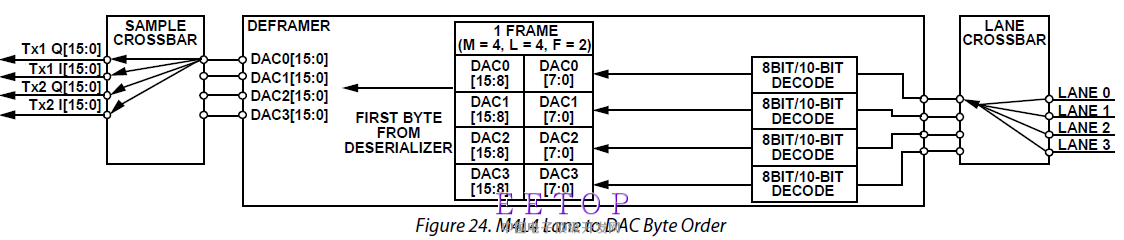

最近在使用JESD204B core,遇到了问题,麻烦做过的大神指点迷津。芯片端的组帧要求为

在FPGA端,输入由DDS产生的4M单音信号,我的组帧顺序为:

tx_core_data[127:112] = {chn2_q(n+1)[7:0],chn2_q(n+1)[15:8]};

tx_core_data[111:96] = {chn2_q(n)[7:0],chn2_q(n)[15:8]};

tx_core_data[95:80] = {chn2_i(n+1)[7:0],chn2_i(n+1)[15:8]};

tx_core_data[79:64] = {chn2_i(n)[7:0],chn2_i(n)[15:8]};

tx_core_data[63:48] = {chn1_q(n+1)[7:0],chn1_q(n+1)[15:8]};

tx_core_data[47:32] = {chn1_q(n)[7:0],chn1_q(n)[15:8]};

tx_core_data[31:16] = {chn1_i(n+1)[7:0],chn1_i(n+1)[15:8]};

tx_core_data[15:0] = {chn1_i(n)[7:0],chn1_i(n)[15:8]};

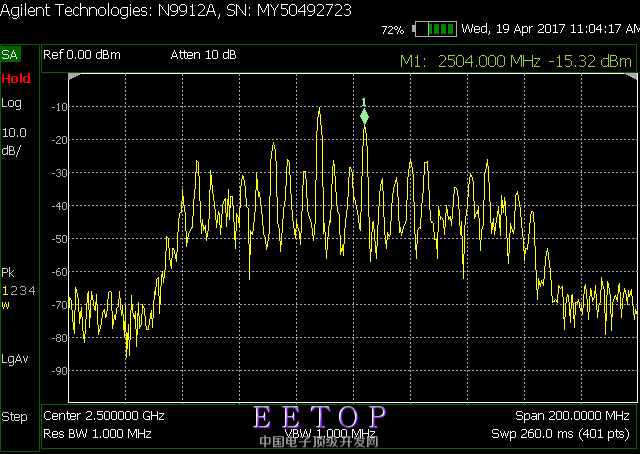

出来的频谱波形如下图:

在FPGA端,输入由DDS产生的4M单音信号,我的组帧顺序为:

tx_core_data[127:112] = {chn2_q(n+1)[7:0],chn2_q(n+1)[15:8]};

tx_core_data[111:96] = {chn2_q(n)[7:0],chn2_q(n)[15:8]};

tx_core_data[95:80] = {chn2_i(n+1)[7:0],chn2_i(n+1)[15:8]};

tx_core_data[79:64] = {chn2_i(n)[7:0],chn2_i(n)[15:8]};

tx_core_data[63:48] = {chn1_q(n+1)[7:0],chn1_q(n+1)[15:8]};

tx_core_data[47:32] = {chn1_q(n)[7:0],chn1_q(n)[15:8]};

tx_core_data[31:16] = {chn1_i(n+1)[7:0],chn1_i(n+1)[15:8]};

tx_core_data[15:0] = {chn1_i(n)[7:0],chn1_i(n)[15:8]};

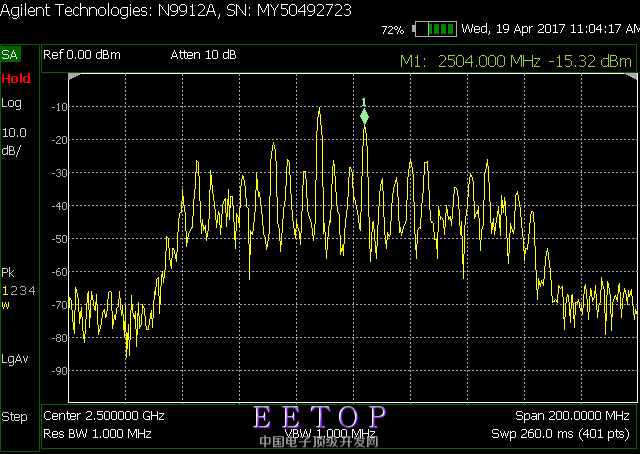

出来的频谱波形如下图:

你想说明什么问题呢? 对还错? 还有你上面的chn2_q这些数据吃从哪里来的呢?

首先谢谢你的回复!我使用DDS产生的单音信号,理论上应该也是出来单音信号,但是现在出来的信号频谱不对。chn2_q(n+1)和chn2_q(n)的关系为一个DDS产生信号前后两个时钟所送出的两个点,chn1与chn2送的数据一致。我采样率为122.88M,而core时钟为61.44M,所以需要把两个DDS的数据组合成一帧送入jesd204b的 IP core。