register

output [n:0] out

reg [n:0]out_reg

input we,rd,clk

always@(posedge clk)

if(we)

output_reg<=in;

if(rd)

out<=out_reg;

end

输入一个2bit的input存到nbit的out_reg

但是我要把所有输入放在reg里面

例如第一个周期输入01>>>out_reg变成01

第二个周期输入11>>>out_reg变成0111

以此类推

请问我该怎么改这个代码

out <= {out[n:2],in};

能写详细点吗 ...这段要放哪个位置呢

就放到你we分支下面,然后rd你要做每次读取out_reg[0:1]出去,out_reg <= {out_reg[2:n],00}这个操作逐渐把out_reg清空,是这样吗?

不是这样的 我要每次传2bit的input给out_reg传n次假设第一次传01 out_reg先存了01

第二次传11这时候out_reg变成0111

传很多次之后rd变成1再把out_reg里的值全部一次丢出去

这是我的代码

但是他失败了 我第一次传01它的out_reg变成0101

第二次传11 out_reg变成1111

module regef(out, in, we,rd, clk);

parameter m=4 ;

input [1:0] in;

input we,rd;

input clk;

output [m-1:0] out;

reg [m-1:0] out;

reg [m-1:0] out_reg;

generate

genvar i;

for(i=0;i<2;i=i+1) begin: out_regen

always @(posedge clk)

begin

if (we)

out_reg[2*i+1 -: 2]<= in;

if(rd)

out<=out_reg;

end

end

endgenerate

endmodule

input[1:0] in

output [n:0] out

reg [n:0]out_reg

input we,rd,clk

always@(posedge clk)

if(we)

output_reg<={(output_reg<<2),in};

if(rd)

out<=out_reg;

end

依然失败

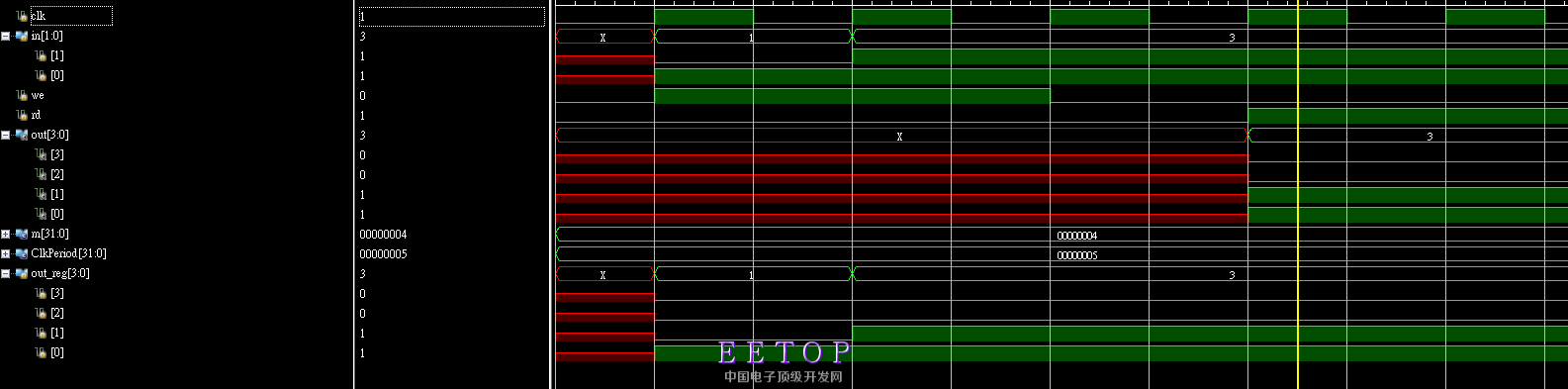

波形

试试2楼的代码放到if(we)下,并且把we和rd两个条件的进程分开来写。有条件的话,最好加上复位条件。

if(!reset)

初始化out_reg

elsif (we)

out_reg <= {out_reg[n:2],in};

if(!reset)

初始化out

elsif(rd)

out <= out_reg;

always的写法省略了。

不好意思,写错了,

output_reg<={(output_reg<<2),in};改为 output_reg<=(output_reg<<2)+in;