关于数字抽取滤波器的直流分量消除和奇次谐波消除的问题求助

时间:10-02

整理:3721RD

点击:

论坛中的各位大神,求教一个问题,我在设计数字抽取滤波器时遇到这样一个问题。

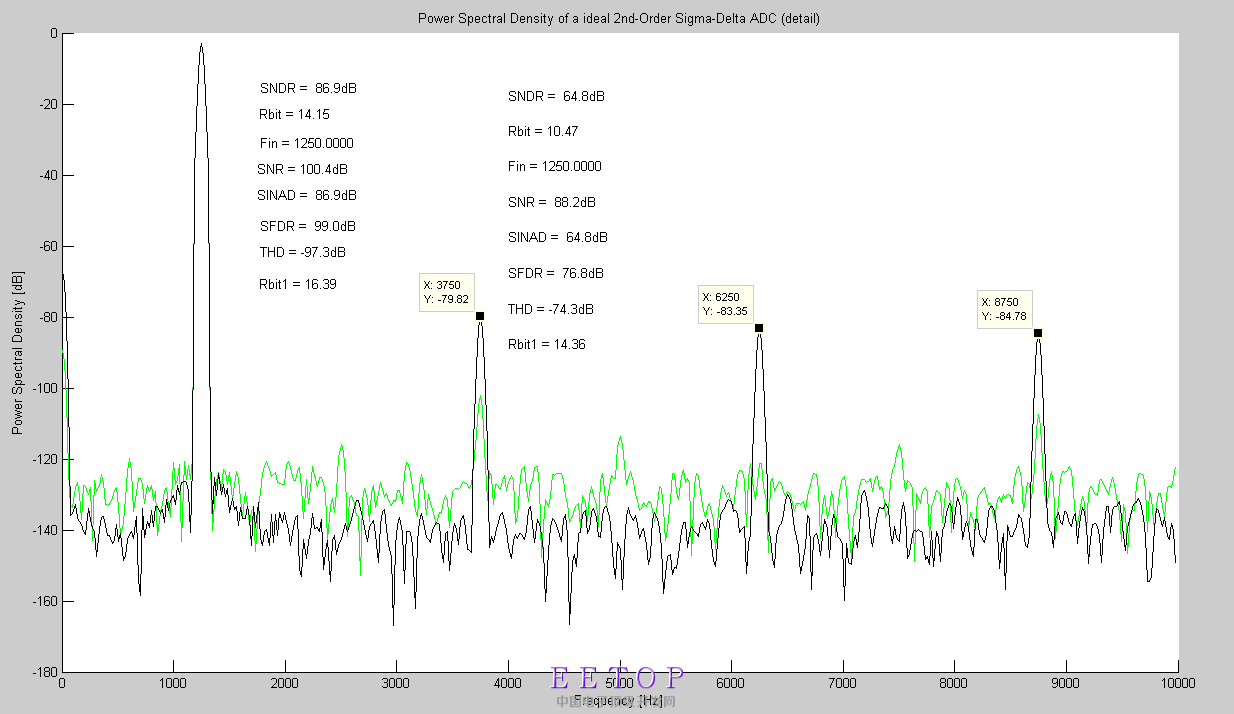

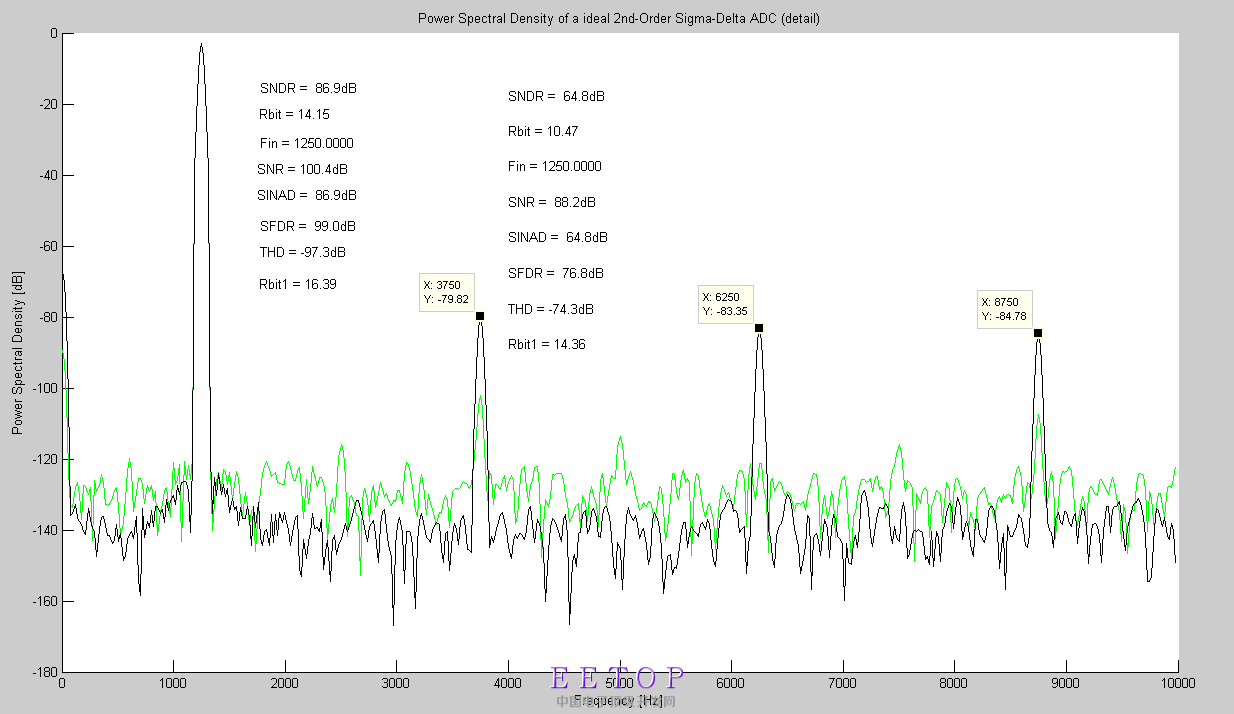

我在用verilog编写滤波器的RTL代码,然后用Modelsim仿真得到滤波器输出数据,对此数据进行频谱分析,发现了两个问题:

1)低频部分的噪底(也可以认为是直流分量)比较高,怎么消除?

2)频谱分析中的奇次谐波分量比较大,这是什么原因导致的?

【注:】[1]上图中,绿色线代表的是Simulink建模的滤波器输出对应的频谱分析图;黑色线代表的是Modelsim仿真的滤波器输出对应的频谱分 析图;

[2]由上图知,Simulink建模时的几次谐波分量比较小。

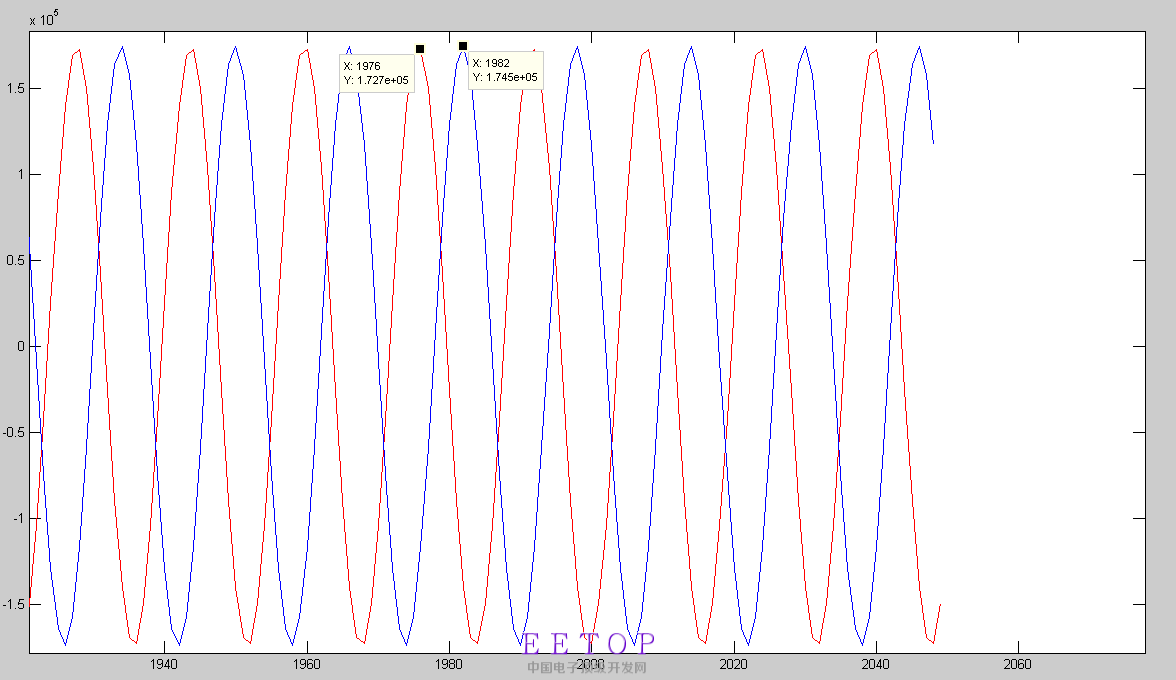

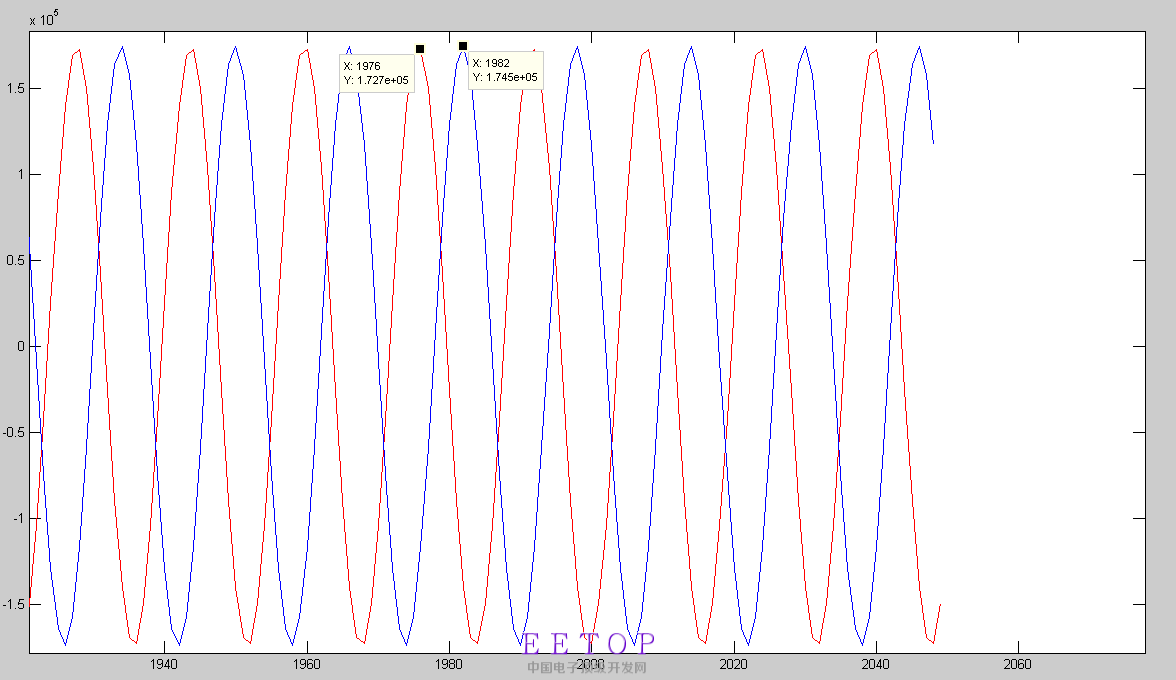

刚开始我认为是RTL代码部分可能有写错的地方,但是我检查代码之后,发现代码没有错误。然后我又分析滤波器输出的Modelsim 仿真数据和Simulink仿真数据,对比图如下所示:

【红色代表Simulink建模数据,蓝色代表Modelsim仿真数据】

【红色代表Simulink建模数据,蓝色代表Modelsim仿真数据】

波形图中不同的地方只有两点:[1]延时不同;[2]波峰和波谷有细微的差别。

………………

目前可能的原因我都想变了,还是没有能解决上面的第2个问题,请群里做过的大神或者懂的大神帮帮忙,给给建议,本人将不胜感激,谢谢啦!

我在用verilog编写滤波器的RTL代码,然后用Modelsim仿真得到滤波器输出数据,对此数据进行频谱分析,发现了两个问题:

1)低频部分的噪底(也可以认为是直流分量)比较高,怎么消除?

2)频谱分析中的奇次谐波分量比较大,这是什么原因导致的?

【注:】[1]上图中,绿色线代表的是Simulink建模的滤波器输出对应的频谱分析图;黑色线代表的是Modelsim仿真的滤波器输出对应的频谱分 析图;

[2]由上图知,Simulink建模时的几次谐波分量比较小。

刚开始我认为是RTL代码部分可能有写错的地方,但是我检查代码之后,发现代码没有错误。然后我又分析滤波器输出的Modelsim 仿真数据和Simulink仿真数据,对比图如下所示:

【红色代表Simulink建模数据,蓝色代表Modelsim仿真数据】

【红色代表Simulink建模数据,蓝色代表Modelsim仿真数据】波形图中不同的地方只有两点:[1]延时不同;[2]波峰和波谷有细微的差别。

………………

目前可能的原因我都想变了,还是没有能解决上面的第2个问题,请群里做过的大神或者懂的大神帮帮忙,给给建议,本人将不胜感激,谢谢啦!

直接对比数据,modelsim数据应该跟simulink数据相差1,从你第一张图和第二张图上看应该是你的滤波器处理有问题。滤除低频信号就要看你信号带宽了,如果低频信号在你有用信号带内的话,用陷波器吧。

非常感谢您的答复,问题已经解决了,是我前面数据采集的问题(前面第一级CIC滤波器的数据输出没有采正确,所以才导致了这个问题)。另外请问您一下,那个多相分解直接型滤波器结构中的求和部分在RTL代码中是采样阻塞赋值还是非阻塞赋值好一些?

顶一下,别沉了——··——》》》》多相分解直接型滤波器结构中的求和部分在RTL代码中是采样阻塞赋值还是非阻塞赋值好一些?

那个谐波问题我也没弄明白原因,小编能解释的清楚一些吗?谢谢了

用阻塞还是非阻塞主要考虑时序。如果你对处理时间延长的要求较低,建议用非阻塞方式,减少不必要的错误