DFF D触发器原理 同步时序设计 RTL

百度百科“D触发器” ,讲D触发器工作原理,有一句“总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。” 其中“三步都是在正跳沿后完成”表示看不懂,请大神帮忙点拨下。

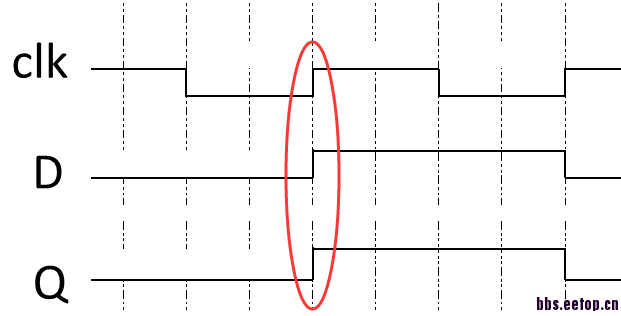

在时钟跳变沿之前x ps,D端要保持稳定,否则setup违例

在时钟跳变沿之后x ps,D端仍需保持稳定,否则hold违例

所以,就存在一个时间窗口,即时钟沿跳变前后,D段不能变化,在这个窗口内,将D端电平传输到Q端上

可以去看一下D-FF的邏輯閘電路,試著去推導一下會更有感覺喲。

追问: 1. 时间窗口的“时间”是什么量级的?

2. 我在做同步电路设计RTL coding时候,通常情况是 “D信号由clk 上升沿触发产生”,然后D信号和clk再经过DFF,为什们我们不用考虑上升沿重叠风险呀?

不是有setuptime 和 holdtime 要求吗,重合肯定不满足啊。

http://blog.chinaunix.net/uid-25553717-id-3286143.html

这个好像有用: http://blog.chinaunix.net/uid-25553717-id-3286143.html

D和CLK上升沿重合,基本上CLK采数据时是会出现问题的,也就是不知道会采到D沿前的还是后的。

如果较个真,在后端的时序里,也有一些库的DFF的hold要求是0,那么D沿和CLK沿重合时采的数据就是0(这时对数据“0”来说,setup和hold满足)

学习了,,,,,,,,,,

谢谢!

学习了

要看输入与clk上升沿的关系,如果是同步的(@posedge clk data赋值),这种情况下data肯定是在clk上升沿之后,所以data肯定是在下个上升沿有效的(或者说下一个clk上升沿才能采到数据);如果是异步的(data和clk上升沿碰巧碰在了一起),data在这个上升沿还是下一个上升沿被采到要看具体仿真器。不过从setup /hold 来说的话最好还是不要在时钟上升沿做数据的变化。

这个数据不能在时钟的上升沿跳转,要满足steup

这个结果是偶然,如果换一种写法或者换一个EDA,结果可能会变