关于DDR3的刷新周期

希望高手指点一下,非常感谢~

tREFI是刷新的平均周期。很多DRAM,常温下每次完整刷新的最小时间是64ms,一次完整刷新指的是把所有ROW都刷新一边。DRAM的每次刷新操作只能对一个ROW刷行,因此tREFI=64ms/row number。

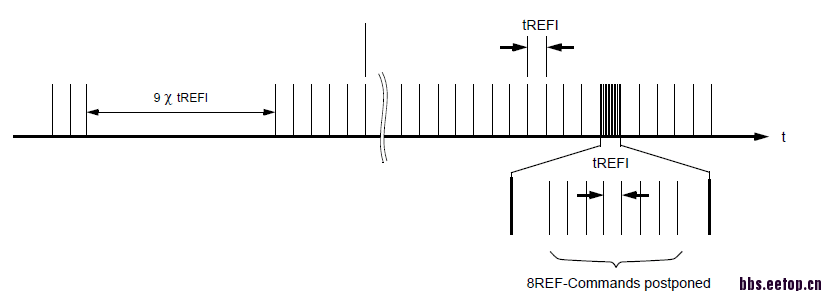

如果前面刷新的慢了,必须要在后面把时间补回来。

明白了,不同的刷新针对的是不同的row,所以前面漏掉的后面才要补上

太感谢了!

一般只要在ddr的spec规定的时间内发出的刷新的总的次数能满足要求就可以了,刷新一次ddr的每个row就加一次

这里为什么要一次发8个或者9个刷新的作用是,该刷新的时候就连续发多个刷新,这样就可以合理的插入read write active等命令,对read write的阻塞作用会一定程度地减小,最终造成数据的吞吐速率增加

同时,刷新前是需要下precharge all这个命令,这样也可以节省多个precharge all的命令个数

明白了,非常感谢!

每次刷新都会对所有逻辑bank都刷新吗?

刷新是平均的。不是必须按照一个间隔 。

同问!

每次刷新刷一行,俺也不知道是一个bank的一行还是所有bank的一行……

感觉应该是所有bank一起刷?

嗯,多谢啦,能否回答一下6楼那个问题?

每次刷行是对所有的bank的其中一个row都刷新一次,也就是每个bank内的控制刷行的计数器都加一次,但是不一定每个bank的row是相同的,所以一般64ms指的是遍历一个bank的时间,所有bank是并行刷新的。

赞,太感谢了!

谢谢解释,解开了我一些关于DDR的疑惑

对于micron的DDR3,有的达到了16K的Row,但是refresh count仍然保持8K,所以我感觉并非一个REF命令刷一个Row。

不知道具体怎么操作的?

标题

这中情况下,刷新周期参数配置要小一半才行。

你是指的我说的这种情况吗?

tREFI降低一半?也就是一般情况的7.8变为3.9?

但是micronde手册上并未这样指出啊?

美光的文档上是有提到7.8(64ms/8192)和3.9 (32ms/8192)但是,这两个参数是针对不同的Tc的,不是针对row的

很好!

不管row的数目,平均刷新间隔tREFI都是7.8us。如果row比较多,那么一个刷新命令就会刷新更多的行,7.8us=64ms/8192得到的,这是跟以前的ddr2/ddr兼容。请注意另一个参数最小刷新间隔tRFC(min),这个参数会随着row的增加而增大,为什么会这样呢?就是因为如果row更多,那么一个刷新命令就要刷新更多的行,那么就要求两个刷新命令之间的间隔更大。

很好,谢谢解释