请问我这个计数器怎么综合后成这样了?谢谢

时间:10-02

整理:3721RD

点击:

module memory(

clk,

rst_n,

clk_out

);

parameter N = 20; //分频器N分频

parameter t = 4; //计数器的位数

//输出端口

output clk_out;

//输入端口

input clk;

input rst_n;

//端口类型声明

reg clk_out;

reg[t-1:0] cnt;

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin //异步复位

cnt <= 4'b0;

clk_out <= 1'b0;

end else if(cnt == N-1) begin //计数到9时,计数器清0,输出翻转

cnt <= 0;

clk_out <= ~clk_out;

end else begin

cnt <= cnt + 1;

end

end

endmodule

clk,

rst_n,

clk_out

);

parameter N = 20; //分频器N分频

parameter t = 4; //计数器的位数

//输出端口

output clk_out;

//输入端口

input clk;

input rst_n;

//端口类型声明

reg clk_out;

reg[t-1:0] cnt;

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin //异步复位

cnt <= 4'b0;

clk_out <= 1'b0;

end else if(cnt == N-1) begin //计数到9时,计数器清0,输出翻转

cnt <= 0;

clk_out <= ~clk_out;

end else begin

cnt <= cnt + 1;

end

end

endmodule

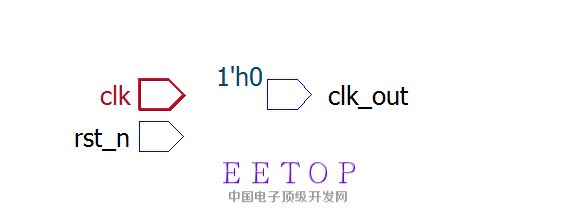

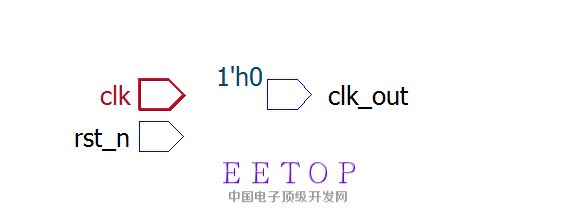

没问题的,只是隐藏了内部计数器,所以输出没有连接

小t 改成5试试, 位宽不够

谢谢,改成5就可以了,可是为什么啊?我的计数器只记到9就行了 4位位宽按理说够了呀

4位怎么到20呢

cnt只计数到9,然后clk_out就翻转了啊?然后cnt清0cnt只从0计数到9啊

你的N =20,哪里9?

额,我错了,少些了/2 ,谢谢各位前辈。