在VCS中对FPGA设计进行仿真

我尝试把Xilinx的库文件都加入到文件列表中让VCS编译后自己去找,但是一直出错啊,如果先编译xilinx的库然后再告诉VCS,应该也是可行的,但是VCS不熟练,不太会,哪位高手提供点思路

做FPGA的就别折腾VCS了

二楼正解,我顶!

VCS还是比MODELSIM块啊,还是用的照的,弄个脚本就好了

做ASIC用VCS和NCverilog比较好,做FPGA还是Modelsim或者questasim,牵涉到FPGA仿真库的问题,不是不可以用VCS,而是用VCS显得不伦不类,至少我没见过做FPGA开发的人用VCS的

目前在公司服务器上面做FPGA设计的仿真,只有VCS可用了

questasim还没有用过的,大家给想个办法。

可以的.

把FPGA的仿真库compile在VCS里面就可以啦.都是verilog的代码,为什么不可以呢,

才vsv

学习啦.

谢谢.

学习啦.

谢谢.

FPGA的仿真模型编译对于VCS和NC-SIM来说不成问题,一般不用的原因还是在于成本,因为这些工具都是在lINUX下运行的,而做FPGA的一般都是在WIN下开发,所以就导致了这个观念,等你的工程大到一定的程度的时候,用单机跑的话需要跑一天的时候,一般都会转移到服务器上去,毕竟这样会快很多,在这种情况下,采用VCS和NC-sim进行仿真的可能性就比较到了,

我觉得WIN下的MODELSIM的能力还是不行,对于大的工程和较长时间的仿真,在WIN下是做不成的,主要是系统的稳定性不行,系统调度内存的能力有限。只能仿真一些小工程和模块级的仿真。

家里的键盘不好用,打字太累了,就这些吧,

放弃VCS,决定用modelsim来仿真了,因为VCS中添加FPGA的仿真库太难了,而且据说FPGA中一些加密的库还不支持,特此声明!

如果有朋友遇到和我一样的问题,建议还是不要在VCS上动脑筋了。

其实很简单的,他和你后仿真的添加库的方式是一样的,使用-y 全路径(到文件夹)这样的方式就可以轻松添加的,

这个可以作为脚本的相对固定的部分,VCS会自动去编译这个库文件下的有用的*.v文件,这样就可以实现仿真了,

你可以尝试一下,如果有问题的话可以给我发消息,我觉得还是VCS比较爽,虽然我在最开始的时候喜欢用MODELSIM,

都是仿真工具。我就没有听说过有modelsim能仿,VCS或是nc-verilog不能的。要么是技术问题,绝对不是工具的问题。专业的工程师肯定觉得linux下写script肯定比你modelsim点击鼠标有效率。楼上的不要误导别人哈。

是有些IP是VCS仿真不到的,我遇到过同一个文件VCS不能仿真,NC可以的,这个很正常,还有ISE对modelsim支持较好,你生产的IP都是给你modelsim的仿真脚本的,不需要自己写。主要还是些IP的问题,如果代码都是你写的,只是调用了FPGA的基本单元库,任何工具都没有问题,只要用 -y +libext+.v 等命令就可以了,如果牵涉到IP,就难弄了。其实VCS也一样,不信你用其他工具去仿真一下 DW_ASYMFIFOCTL_IN_WAPPER(这个库是dc中的一个库文件),其他工具仿真不了

还有就是ISE工程中有些是VHDL的,你要仿真非得要VCS-MX才可以,麻烦一点,自己学习的话,还是哪个顺手用那个,毕竟只是工具而已。用哪个都一样,在公司都有现成的脚本的。

好的,这些的确是有问题(只是可能,我没有时间一个一个试)。但是各位在设计的时候有没有想过自己的代码要在什么平台上都能跑呢?就像大家喜欢linux一样,因为其兼容性好。当我们在大骂别人的兼容性不好的时候,有没有想过自己在设计的初期有没有研究过这些问题。有没有想过我现在在FPGA上跑的文件,过几个月,过一年有可能需要做成ASIC?

所以放开你的眼见,这些就不是问题啦。

FPGA产品做成ASIC要看怎么做了,你不可能把DCM用到ASIC,或者NOSII核用到ASIC,或者MB用到ASIC,这些都是要替换成相应的ASIC IP,你替换成synopys的IP,你最好要用Synopsys公司的仿真工具,如果是cadence的,当然最好是candence。就是是ASIC的原型验证也讲究个等效替换,而不是拿来就用。不是怪兼容性有问题,而是在相应的情况下采用相应的工具而已。

美光公司的SDRAM仿真模型,用vcs不可以,不是库的问题,而是说模块太大,而用ncverilog就可以,你可以自己试试看

VCS工具不错的,只是本人目前应用不熟练而已,没有一款完美的工具,大家不必在工具好坏上争论了,公司有什么工具就用什么工具啦

在Modelsim中一样可以用脚本,不一定非要什么都点鼠标。用Modelsim很多情况下都是因为ip的原因。在linux下用ISE,Quartus,Modelsim,Questsim一样很方便~

呵呵,辛苦啊

后记:

现在已经用VCS来仿真FPGA了,个人感觉VCS挺好用的,尽管刚开始时命令老是用不好,不过速度似乎比MODELSIM快些,而且脚本写好后就不用来回改了,调试起来方便了很多

请问哈要调用xilinx的库,vcs下如何设置呢。?

在VCS的command line里加上xilinx的库

-y xilinxlibpath

其中xilinxlibpath 是你xilinx仿真库unisims,xilinxlibcore,simprims的路径

高见啊。

谁说的modelsim不能用脚本,do和tcl不行吗?但是Makefiel不行,请牛人指点一下

得到的得到的得到的地对地导弹

VCS有综合的功能吗?DC综合后仿真,属于后仿吗?

曾经在windows平台下用过modelsim的命令行形式,当时的做法是把一些编译仿真步骤写成.do格式的文件专门用于vsim,vlog 来调用,外面用批处理命令来调用vlog和vism ,感觉也不错,脚本写好,就不用来回改

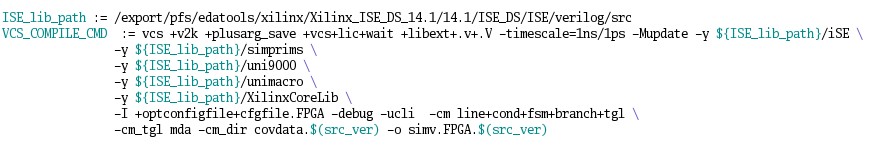

您好,向您请教一个问题,用VCS仿真FPGA的设计,在VCS中添加ISE的库,在VCS的Makefile脚本中我添加了如下的库,

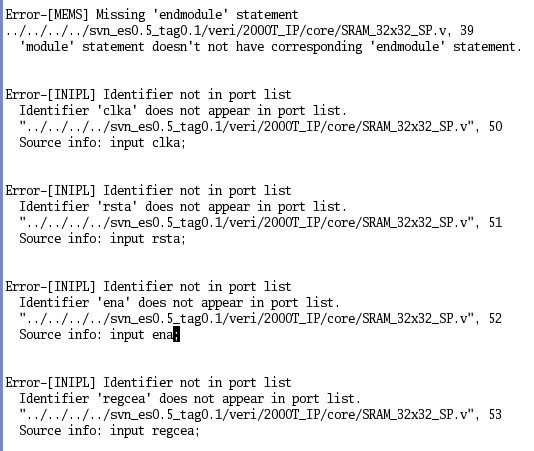

然后再仿真的时候出现了如下错误,

这个是我在ISE中生成的一个RAM的IP核,用VCS仿真编译的时候就出现找不到这个文件的端口列表,但是这个RAM的*.v文件是ISE自动生成的,端口列表什么的都是有的,那么现在出现了这线的错误提示,是因为什么原因呢,是在VCS中添加ISE的库出了问题,还是除了添加ISE的库文件之外还需要添加什么文件或命令什么的吗?

请高手指导一下!非常感谢!