XILINX FPGA复位

时间:10-02

整理:3721RD

点击:

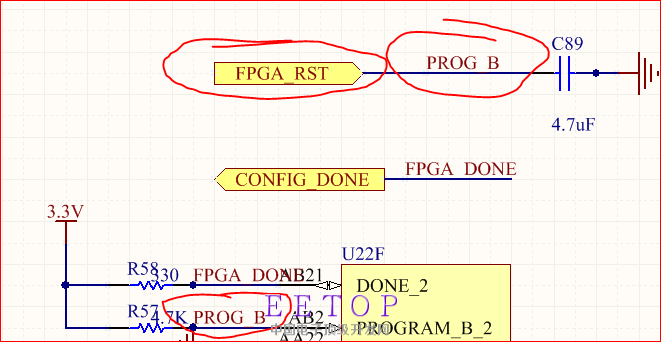

请教大家一个关于FPGA复位问题,对于代码中常编写的always @ (posedge clk or negedge rst_n)中的rst_n是连接外部复位引脚的吧,

但是从我这电路图中看,并没有连rst_n管脚,只有一个外部管脚连接到 PROGRAM_B_2管脚,

问题:

1,这个管脚输入不需要写入语言代码中吧?(我给分配管脚时,无法锁定);

2,是不是意味着这没有外部复位,所以就不能使用rst_n?

这个得看PROGB是否连接到FPGA芯片的IO上吧,你这个图也看不出来是否连接到FPGA芯片的IO上啊,如果连接上那管脚应该就能锁定吧

win10终于可以完美支持啦!亲测!

这是两个概念吧,你的原理图上FPGA_RST是上电以后自动下载FPGA的bitfile,而我们逻辑里面用的reset是给内部逻辑用的,一般需要外面定义一个根pin。

谢谢! 图中U22是FPGA芯片,连接的是专用管脚PROGRAM_B_2。专用复位管脚,无法锁定.

恩,谢谢你,我这样理解,那个是专用复位管脚,不要语言描述,如果外部没有其他复位管脚,那就不能使用RST_N,是这样的吧

666

学习到了。

program_b是上电加载程序的复位,拉低一次FPGa就重新加载一次配置文件