调用XILINX的IP核在Modelsim中不能进行功能仿真,为什么?

亲,把错误信息贴上来看下。 这样问,严重考验我的想象力。

# vsim -voptargs=+acc work.trigger_fifo_top_tb

# ** Note: (vsim-3812) Design is being optimized...

# ** Error: E:/ISE_PROJECT/trigger_fifo/fifo_generator_v6_2.v(198): Module 'FIFO_GENERATOR_V6_2' is not defined.

# Optimization failed

# Error loading design

Optimization failed <--- 麻烦把modelsim这个功能关掉,这样:

vsim -novopt work.trigger_fifo_top_tb glbl

在xilinx安装目录下去找一个glbl.v的文件,拷贝到你的仿真目录下,跟其他.v文件一起编译。

试一下看还报不报错,有错再贴上来。

[attach]431523[/attach]回复 2# catcat_2

在ise中的文件层级关系是这样的如图所示,inst文件缺少,不知道该从哪里添加,但是在没有该文件的条件下,功能仿真是可以通过的,单独在Modelsim中进行仿真时出现的错误,我估计是与这个inst有关~但不知如何解决,求指导!

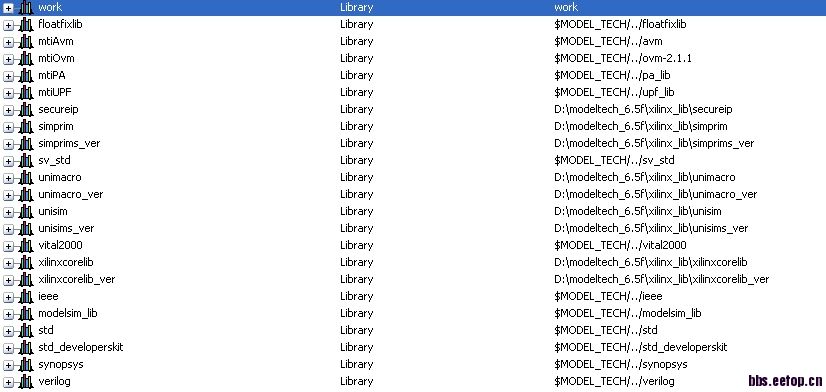

对了,你要先确认下你单独用modelsim的时候,是不是xilinx的库都加载了。看看modelsim那个library页选项卡里面是不是有所有的xilinx的lib

vsim -novopt work.trigger_fifo_top_tb glbl

# Refreshing D:\modeltech_6.5f\examples\work.trigger_fifo_top_tb

# Loading work.trigger_fifo_top_tb

# Refreshing D:\modeltech_6.5f\examples\work.trigger_fifo_top

# Loading work.trigger_fifo_top

# Refreshing D:\modeltech_6.5f\examples\work.trigger

# Loading work.trigger

# Refreshing D:\modeltech_6.5f\examples\work.fifo_generator_v6_2

# Loading work.fifo_generator_v6_2

# ** Error: (vsim-3033) E:/ISE_PROJECT/trigger_fifo/fifo_generator_v6_2.v(198): Instantiation of 'FIFO_GENERATOR_V6_2' failed. The design unit was not found.

# Region: /trigger_fifo_top_tb/uut/fifo1

# Searched libraries:

# D:\modeltech_6.5f\examples\work

# ** Error: (vsim-3170) Could not find 'D:\modeltech_6.5f\examples\work.glbl'.

# Error loading design

# Optimization canceled

所有的库都有,就是不知道这些库是否正确,有些库里的文件夹名字都是@@@@这样的形式

汗。 没看到图。 图挂了。

不过错误信息明确了,应该是少了库,还有glbl.v文件没有加进去。

你看看库是不是没有被modelsim加载进去。看modelsim的library那一页有没有一个unisim 和 simprim库。

还有 XilinixCoreLib 这个库有没有在modelsim的library那一页里面。

看看这些库后面path那一项是不是正确的。

那两个库都有,我在XILINX安装目录下没有找到*.glbl文件,怎么办?

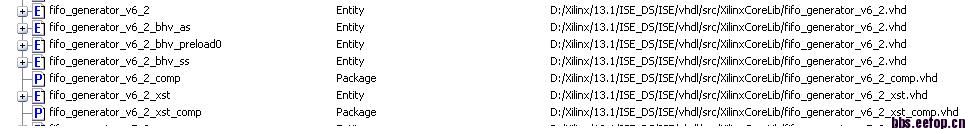

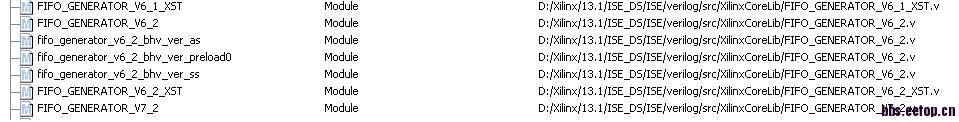

那把XilinixCoreLib 这个库展开,看看里面的fifo_generator是什么版本的。

按这个路径去找一下,看看有没有。*****Xilinx\x.x\ISE_DS\ISE/verilog/src/glbl.v

你的ISE是哪个版本的?

把xilinxcorelib_ver 这个库展开,看看里面的fifo_generator是什么版本的。是不是和你的v6.2的版本对应不上?

vsim -voptargs=+acc work.trigger_fifo_top_tb

# vsim work.trigger_fifo_top_tb

# ** Note: (vsim-3812) Design is being optimized...

# ** Error: E:/ISE_PROJECT/trigger_fifo/fifo_generator_v6_2.v(198): Module 'FIFO_GENERATOR_V6_2' is not defined.

# Optimization failed

# Error loading design

添加了glbl.v文件后编译结果,在哪里关闭Optimization这项功能?把那个 -voptargs=+acc 换成 -novopt。 就是这样

vsim -novopt work.trigger_fifo_top_tb glbl

记得加glbl。 还有,我感觉你这个问题貌似是modelsim在search的时候只搜索了work目录,所以它找不到你的fifo_generator_v6_2。

你要不尝试一下在编译之前用vmap命令把那个xilinxcorelib_ver重新map一下

vmap xilinxcorelib_ver xilinxcorelib_ver

实在不行,你就只能把xilinxcorelib_ver这个库编译到work库里面了,这招肯定必杀。 就是很烦躁。对了,把Modelsim根目录下面的“modelsim.ini”中“VoptFlow=1”改为“VoptFlow=0”。 改之前要把modelsim.ini的只读属性去掉。

我觉得也是只是在work文件加下进行的,他找不到我的xilinxcorelib,

你这样试一下呢,强制加载那个库:

vsim -novopt -t ps -L xilinxcorelib_ver work.trigger_fifo_top_tb glbl

-L 是大写的L,加载verilog仿真库的意思。你可以参看modelsim user's manual 里面有介绍

我以前也碰到过这种破事。 最后就是把那个库直接编译到work里面解决的。

如果是vhdl的,那还好改,看看这个*.vhd文件的顶层用 use 调用的 library 是从哪开始找的,直接改掉就是。verilog 里面没有这个东西,所以不知道怎么去切换它的搜索路径。

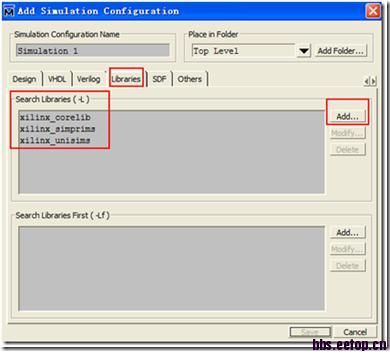

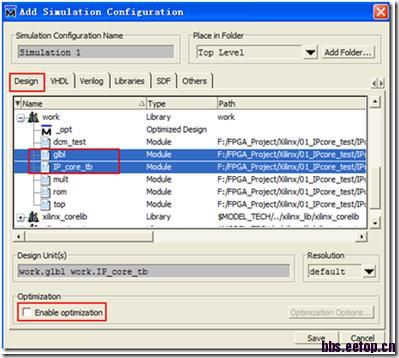

问题已解决,非常感谢您的热心帮助。是这样的我没有设置Simultion Configuration,在这里应该设置Library为您说的那三个仿真库,还有就是不勾选Enable Optimistion选项。

OK。搞定就好。

用那个-L 选项也可以解决这个问题。都是一样的。你以后可以多用用命令行,比GUI更方便的。给你一个速查手册,谷歌一下“modelsim 6.4 quick guide”,直接下那个PDF就可以。

感谢您的热心帮助~今天看了这个帖子,受益匪浅,谢谢前辈们

可以考虑VSIM命令后加-L XilinxCoreLib等,把库加进来。

在.v文件中例化后用Modelsim仿真,仿真结果不对啊,在测试代码中要做什么更改吗?

good 厉害 多谢 好贴

老师好,我想请教一下,我在modelsim中已经编译好xinlinx核以后,新建verilog文件调用核怎么写这条语句呢?比如以前在VHDL中使用for all:wrapped-lpf use entity XilinxCoreLib.fir_compiler_v5_0(behavioral)调用核。谢谢!