对老生常谈的话题hold time violation的个人理解还有疑惑

好吧,hold time violation这个话题基本上已经味同嚼蜡了,但是怎么能解决这个问题呢?紧紧从timing issue的角度考虑?

以下是我对hold time violation的认识

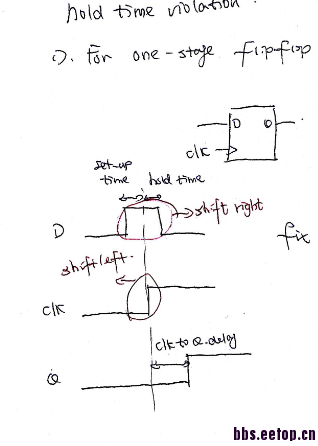

1> 如果只是考虑一级pipeline的话,也是最常见的面试题啦

(画得不好不要笑,新人另外求画图软件),在这种情况下,如果发生hold time violation的话,那我们就要想办法延长clk上升沿之后data的保持时间。有两种方法,

1> 加大输出data的combination logic 的延迟,使得data整体右移;

2> 想办法把clk左移,怎么弄呢,减少clock skew(这个是物理现象貌似是不可改变的),减小时间周期?或是在后端设计时把连这个clk的buffer去掉?

此种情况解决hold time violation的方法欢迎讨论,这里仅仅是抛砖引玉。

第一种情况是大家都讨论烂了的,第二种情况我至今没有想到解决方法,

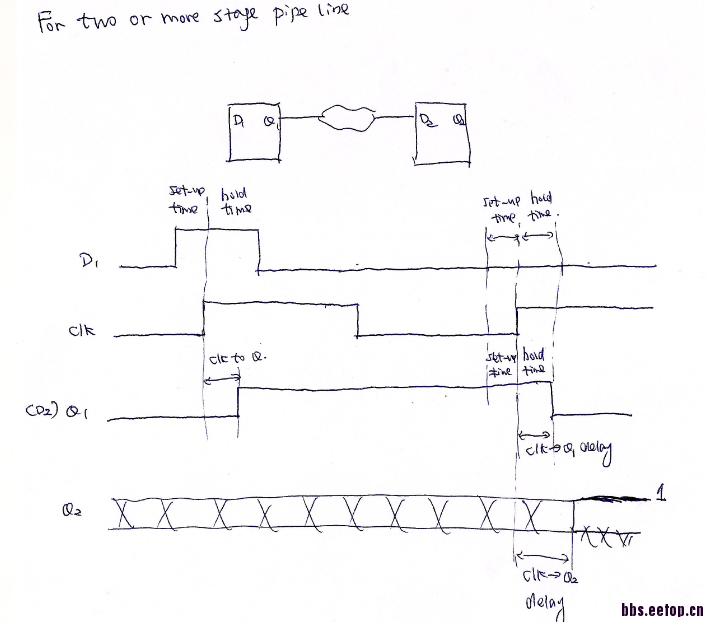

下面是第二种情况,多级pipeline,我们以两级reg为例

在这种情况下,我们把注意力集中在第二个dff,由于Q1同时也是D2,而D2的hold time其实完全是由clk->Q1来决定的,这样的话上述两个方法都无法解决此种情况下的hold violation。

请高人解决下这个问题,难道library 里的Dff 都默认hold time < clk to Q delay ?

@

陈涛

一般来说clk的延迟不容易变,那就修改数据就可以了。一般来说延后一点就可以了。

D2的holdtime是由clk->Q1,组合逻辑延迟,两个dff的时钟走线差,三者决定的。

画时序可以使用 time designer或者visio

两个寄存器之间的时钟延迟差,是由寄存器的位置决定的,可以通过约束两个寄存器的位置来改变。

哥们你好,不知道你是在那一步去解决的这个问题,综合 还是pr的时候,一般我的做法是在pr的时候,将该d触发器的时钟树做短一些

Clock Mesh基本没有Hold Time问题,FPGA里的Global Clock也是Clock Mesh。

Clock Tree的话,Hold is not Setup这篇Paper已经讲的很完整了。除了Scan Reorder部分略坑爹以外。

在第二个例子中,

我觉得D2的holdtime, 你所提到的组合逻辑延迟(也就是两个flipflop之间的logic)是跟它是没有任何关系的,如果combination logical 延迟过大,那D2的setup time都满足不了,而setup time的满足是分析hold time的前提。

而clock skew 和clock jitter也跟hold time没有任何关系,因为D2的由1->0的时间完全取决于clk->Q1的delay,而skew和jitter只是让整个d2的变化往左或者往右平移而已,并不能加长原有hold time的宽度。

欢迎讨论。

clock mesh是什么意思?请指点

多驱动的时钟网络,可以达到更低的Skew(特别是由于OCV造成的Skew),但费电。

补充第三点,3>在data path 后加buffer,是clock 上升沿后old data保持的时间更久。

第三种方法其实就是第一种方法。

解决hold villation问题,无非是你所说的前两种方法,一个方法是加大数据延时,一种方法是减少clock延时。

这两种方法从理论上来讲都是可行的,但应对的情况有所不同。

对于一个新的设计,综合的网表送给后端之后,layout需要做的一个重要步骤就是CTS(clock tree 生成),对于简单的时钟,工具能够很容易应对,但如果时钟关系比较多,比如中间有很多gate clock,那么CTS生成的tree质量就不是那么好了,这时候比较容易产生hold,所以CTS之后都要检查clock的skew,如果太大只能重建CTS。

在进行STA分析的时候,一般是先解决setup问题,后解决hold问题,hold问题解决完的时候一般都是到了要tapout的时候了,最后一段时间如果发现有hold问题,一般会选择在满足setup的情况下将数据往后推,只有万不得已的情况下才会选择动时钟,因为时钟改变不仅影响本级DFF的时序,还会影响下一级DFF的时序。

回答你的一个问题,“难道library 里的Dff 都默认hold time < clk to Q delay ?”

这个答案一般是成立的,比如使用 standard cell搭建一个移位寄存器链,一般情况下,是不需要在两个DFF之间插入额外的cell来保证hold,只要CTS做的比较balance,就不会有问题。(有个别的厂家,e.g. UMC,提供的库是做不到这一点的,需要在DFF之间插入DEL cell将data推迟来保证hold,这样的并不多见)

数据到达下级寄存器比时钟skew还要短才会有hold违例吗?

嗯嗯,学习了

看不懂,插入负边沿reg也能提供1/2周期的保持时间吧?

哈哈,看了小编画的图,笑惨了

学习了

共同关注!

9楼、10楼说的在理,一般加入buffer是可以解决hold问题的

满足的飘过!

哥们,你画的图可以,像外国人画的。 FPGA 内部的 DFF 到 DFF 这个基本是芯片等级决定的。 这个之间的逻辑不要弄太大一般没什么问题。 如果逻辑很复杂,自己多嵌几个寄存器分散到逻辑中

学习了~赞!

看看 谢谢!

好东西