oddr2后面接一个OBUF用来输出时钟,但是输出管脚上没有信号

整个通路是pin(50Mhz)——BUFG——PLL_base——一个生成方波的分频模块——ODDR2——OBUF

器件是Spartan6 LX9

输出个几十M的时钟都搞不定,十分闹心啊

恳请各位大侠帮助,多谢了!

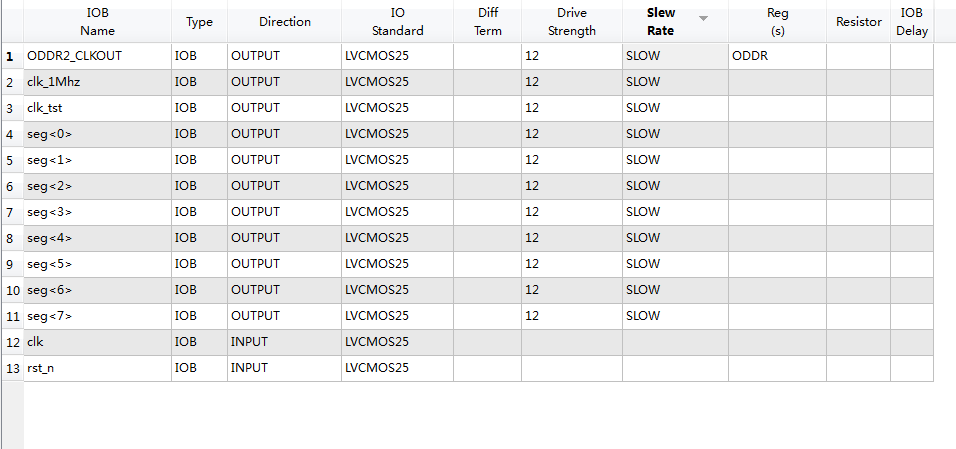

你看看 iob的报告,那个引脚有没有用到

这种方式很常用的啊,检查下输入,管教分配,PLL锁定

谢谢大侠相助,我是初学的小白,你说的IOB是这个吗?

从这看应该是用到了啊。

谢谢帮助,请问如果用oddr2输出上百M的时钟,是不是引出到任何一个可用的IO管脚都可以?我记得在哪看到过是可以的啊,或者说Spartan-6有没有专门的适合作为高速时钟输出的引脚?谢谢了!

从你的IOB报告来看,是用到了输出引脚。能否把你的map warning message贴出来看看

对的,没有专用输出管脚,普通管脚就可以了。而且用ODDR来输出时钟,在源同步接口设计时,推荐这么用的,这一点肯定没问题

时钟通过ODDR输出,在FPGA中ODDR会被放在IOB中,这样输出的时钟能保证相位和clk保持一致!

之前也是遇到这样的问题,是时钟引脚不对

我也遇到类似的问题,我用SPARTAN-6 XC6SLX9,在调用PLL后想要输出其得到的时钟到外部,就必须加ODDR2,我是小白,只好回去看SELSCT io手册,现在还在继续学习这块时钟管理。看了好多,有人说Xilink的是不可以直连到IO资源的,需要一个缓冲驱动,还有说在UCF文件约束中加上

PIN "U_CLOCK_PLL/clkout1_buf.O" CLOCK_DEDICATED_ROUTE = FALSE;

PIN "U_CLOCK_PLL/clkout2_buf.O" CLOCK_DEDICATED_ROUTE = FALSE;

几条约束就好。正号遇到这个问题,等我看完,再来补充。

看完没有,怎么才好。我的输出50m就是正弦波了,怀疑哪里出错了。